- PRODUCTS

- RECORDERS

- SUPPORT

| Home > Pipeline Newsletters > Pipeline Newsletter Model 71622 |

| |||

|

Summer 2011 Vol. 20, No. 2 | |||

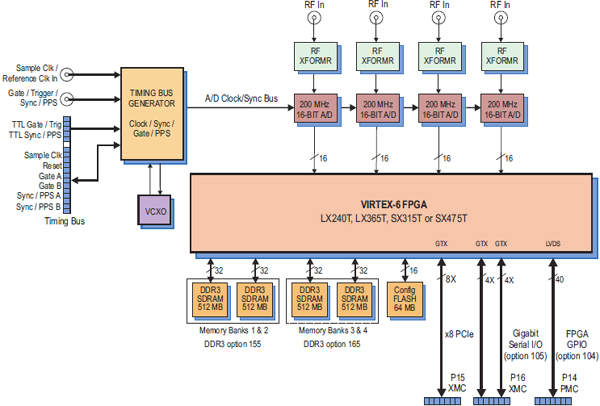

32-Channel Digital Downconverter with four 200 MHz, 16-bit A/Ds and Virtex-6 FPGA - XMC

Model 71662 General InformationThe Model 71662 is a member of the Cobalt® family of high performance XMC modules based on the Xilinx Virtex-6 FPGA. This fourchannel, high-speed data converter with programmable DDCs (digital downconverters) is suitable for connection to HF or IF ports of a communications or radar system. Its built-in data capture feature offers an ideal turnkey solution as well as a platform for developing and deploying custom FPGA processing IP. The Cobalt ArchitectureThe Pentek Cobalt architecture features a Virtex-6 FPGA. All of the board's data and control paths are accessible by the FPGA, enabling installed functions including data multiplexing, channel selection, data packing, gating, and triggering. The Cobalt architecture organizes the FPGA as a container for data processing applications where each function exists as an intellectual property (IP) module. Each member of the Cobalt family is delivered with installed applications ideally matched to the board's analog interfaces. The 71662 installed functions include four A/D acquisition IP modules. Each of the four acquisition IP modules contains a powerful, programmable 8-channel DDC installed IP core. IP modules for control of all data clocking, synchronization, gate and trigger functions, a test signal generator, voltage and temperature monitoring, DDR3 SDRAM memory controllers, and a PCIe interface complete the installed functions and enable the 71662 to operate as a complete turnkey solution without the need to develop any FPGA IP. DDC IP CoresWithin each A/D Acquisition IP Module is a powerful 8-channel DDC bank. Because of the flexible input routing of the A/D Acquisition IP Modules, many different configurations can be achieved including one A/D driving all 32 DDC channels or each of the four A/Ds driving its own DDC bank. Each of the 32 channels has an independent 32-bit tuning frequency setting that ranges from DC to ƒs, where ƒs is the A/D sampling frequency. All of the 8 channels within a bank share a common decimation setting that can range from 16 to 8192, programmable in steps of 8. For example, with a sampling rate of 200 MHz, the available output bandwidths range from 19.53 kHz to 10.0 MHz. Each 8-channel bank can have its own unique decimation setting supporting a different bandwidth associated with each of the four acquisition modules. The decimating filter for each DDC bank accepts a unique set of user-supplied 18-bit coefficients. The 80% default filters deliver an output bandwidth of 0.8*ƒs/N, where N is the decimation setting. The rejection of adjacent-band components within the 80% output bandwidth is better than 100 dB. For more information and a price quotation on the Model 71662, click here.  | |||

|

| CONNECT ON SOCIAL: |

|

|

|

|