# 2-Channel 250 kHz to 70 MHz A/D Converter VME Boards

### **Features**

- Front ends for Pentek Digital Receivers

- Front ends for Pentek 6099A Buffer Memory

- Front panel TTL, ECL, or FPDP outputs compatible with Pentek receivers

- Shielded construction reduces noise

- Internal or external sampling clocks to 70 MHz

- Single slot 6U VMEbus boards

### **General Information**

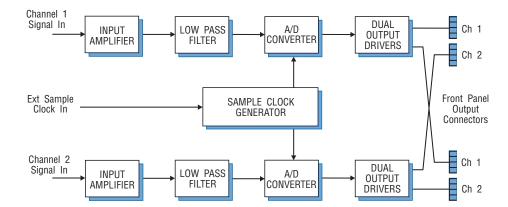

These models are dual channel high-speed A/D converter boards which operate at sampling rates up to 70 MHz. They are single-slot VMEbus boards, and include signal conditioning and clock generation circuitry. The two channels are identical and operate from the same sample clock.

Among their other uses, these models are intended as front ends for Pentek's Digital Receivers and the Model 6099A Buffer Memory. Connections between the A/Ds and the receivers or buffer memory are made with standard 80-conductor 0.025 in. pitch flat ribbon cable (68-conductor cable in Model 6472) using the mating connectors supplied. Complete cable assemblies are also available from Pentek.

# **Signal Conditioning**

All models, except the 6402, accept a  $\pm 1.0$  V full scale analog input signal from a front panel SMA connector with 50 ohm input termination. Model 6402 accepts  $\pm 5.0$  V full scale signal with 100 kohm input termination.

A buffer amplifier then delivers the signal to a high-order Chebyscheff low pass anti-aliasing filter, which restricts input bandwidth to approximately 40% of the maximum sampling rate of each model. Other filter characteristics are available on special order.

For systems in which the input signal is already bandlimited, the on-board antialiasing filter can be bypassed.

### A/D Conversion

The A/D converter resolution and maximum sampling frequency depend on the model. In summary, the available resolutions and frequencies are as follows:

| Model | Resolution | Frequency |

|-------|------------|-----------|

| 6402  | 16 bits    | 250 kHz   |

| 6410  | 14 bits    | 10 MHz    |

| 6420  | 14 bits    | 20 MHz    |

| 6441  | 12 bits    | 41 MHz    |

| 6465  | 12 bits    | 65 MHz    |

| 6472  | 10 bits    | 70 MHz    |

Digitized data from both channels are available on each of two front panel connectors. Two separate sets of drivers are provided for each channel to support more flexible connections to different configurations of digital receivers.

## **Sampling Control**

The sample clock generator includes a crystal oscillator set at the maximum sampling frequency of each model. Model 6472 has 25 and 50 MHz crystal oscillators, in addition to 70 MHz. All oscillators are in standard DIP packages and are easily replaceable by the user for special frequency requirements.

An external sample clock can also be supplied through a front panel SMA connector. Selection of any of the internal oscillators or the external clock is made with on-board jumpers.

### **VME Interface**

The VMEbus interface is used only for power and no VMEbus signals are used on the board.

# **Block Diagram, All Models**

# 2-Ch. 250 kHz to 70 MHz A/D Converter VME Boards

**Ordering Information** Model Description 6402 2-Channel 250 kHz 16-bit A/D Converter, TTL outputs Options: -002 ECL outputs; Input: ±1.0 V full scale -008 FPDP outputs 6410 2-Channel 10 MHz 14-bit A/D Converter, TTL outputs Options:

FPDP outputs

2-Channel 20 MHz 14-bit A/D Converter,

ECL outputs

TTL outputs

Option:

-008

-002

6420

-008 FPDP outputs

6441

2-Channel 41 MHz 12-bit A/D Converter, TTL outputs

Options:

-002 ECL outputs -008 FPDP outputs

6465 2-Channel 65 MHz 12-bit A/D Converter,

ECL outputs

Option:

-008 FPDP outputs

6472 2-Channel 70 MHz 10-bit A/D Converter,

ECL outputs

Option:

-009 ±1.0 V full scale input

## ➤ Specifications, Model 6402

**Input:** single-ended ±5.0 V full scale, 100 kohm input impedance

Anti-aliasing filter: DC to 100 kHz, ±2.0 dB passband flatness, 150 kHz stopband with > 50 dB attenuation; may be bypassed

A/D converter: 16 bits, 250 kHz max. sample rate (ADS7811); harm. distortion <-85 dB, SINAD >80 dB, spurious <-80 dB

Sampling clock: internal 8 MHz crystal oscillator with divider; user installable DIP TTL/ECL oscillator; external TTL clock through front panel SMA connector

# Specifications, Model 6410

**Input:** single-ended, ±1.0 V full scale, 50 ohm input impedance

Anti-aliasing filter: DC to 4 MHz, ±2.0 dB passband flatness, 5.5 MHz stopband with >50 dB attenuation; may be bypassed

**A/D converter**: 14 bits, 10 MHz max. sample rate (Edge Technology ET2471); SNR >67 dB, SINAD >65 dB, spurious components –80 dB

Sampling clock: internal 10 MHz crystal oscillator, or user installable DIP TTL/ECL oscillator; external TTL clock through front panel SMA connector

# Specifications, Model 6420

**Input:** single-ended, ±1.0 V full scale, 50 ohm input impedance

Anti-aliasing filter: DC to 8 MHz, ±2.0 dB passband flatness, 12 MHz stopband with >50 dB attenuation; may be bypassed

A/D converter: 14 bits, 20 MHz max. sample rate (Edge Technology 2473); SNR > 75 dB, SINAD > 72 dB, spurious components < -80 dB

Sampling clock: internal 20 MHz crystal oscillator, or user installable DIP TTL oscillator; external TTL clock through front panel SMA connector

## Specifications, Model 6441

Input: single-ended ±1.0 V full scale, AC-coupled with 10 kHz high-pass cutoff, 50 ohm input impedance

Anti-aliasing filter: DC to 16 MHz, ±1.0 dB passband flatness, 24 MHz stopband with >50 dB attenuation; may be bypassed

A/D converter: 12 bits, 5 MHz to 41 MHz sample rate (AD 9042); SNR > 50 dB, SINAD > 60 dB, spurious components -70 dB

Sampling clock: internal 40 MHz crystal oscillator, or user installable DIP TTL oscillator; external TTL clock through front panel SMA connector

# Specifications, Model 6465

**Input:** single-ended ±1.0 V full scale, AC-coupled with 10 kHz high-pass cutoff, 50 ohm input impedance

Anti-aliasing filter: DC to 26 MHz, ±1.0 dB passband flatness, 38 MHz stopband with >50 dB attenuation; may be bypassed

A/D converter: 12 bits, 5 MHz to 65 MHz sample rate (AD 6640); SNR >50 dB, SINAD >60 dB, spurious components -70 dB

**Sampling clock:** internal 64 MHz crystal oscillator, or user installable DIP TTL oscillator; external TTL or sine (2.0 V p-p) clock through front panel SMA connector

## Specifications, Model 6472

**Input:** single-ended, ±1.75 V full scale, 50 ohm input impedance

Anti-aliasing filter: DC to 30 MHz, ±1.0 dB passband flatness, 45 MHz stopband with >50 dB attenuation; may be bypassed

**A/D converter**: 10 bits, 70 MHz max. sampling rate (AD 9060); harmonic distortion <-59 dBc, IM distortion <-70 dBc, SNR >55 dB

Sampling clock: internal 25, 50, and 70 MHz crystal oscillator, or one of three user-installable DIP ECL oscillators; external TTL, ECL or sine (1.0 V RMS) clock through front panel SMA connector

## **Specifications, all Models**

**Power:** 1.0 A at +5 V; 0.75 A at +12 V; 1.0 A at -12 V

Size: standard 6U VMEbus board, single slot; board 160 mm (6.3 in.) x 233.5 mm (9.2 in.), panel 0.8 in. wide