# MIX-VME Baseboards/Embedded Controllers

#### **General Information**

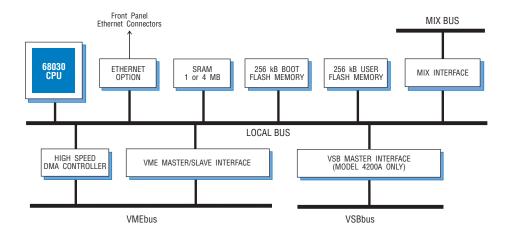

Models 4200A and 4201A convert standard-size Pentek MIX modules into single-slot VME boards with full-featured VME and VSB bus interfaces.

Model 4200A features VMEbus, VSBbus and MIX bus interfaces. The VME and MIX interfaces support both master and slave operation, while the VSB interface supports master operation only. Model 4201A is identical to the 4200A, but without the VSB interface.

#### **On-Board Processor**

Models 4200A and 4201A feature a 40 MHz 68030 processor which manages the VME interface and DMA controller.

The 1MB SRAM is expandable to 4MB and acts as a work area for the 68030 and for DMA transfers from MIX modules. It can also be used for downloading custom routines from a VMEbus host.

The 68030 has full memory access to the MIX bus, the VMEbus and the VSBbus with 32-bit data and address support for all transfers.

Two 256 kB flash memories are supplied: one contains factory-supplied firmware to initialize the board and provide easy-to-use register-based drivers for the DMA controller; the other flash memory is available for user-defined applications.

#### **VMEbus Interface**

The VMEbus interface is implemented with the Cypress VIC and VAC interface chip set which provides well-defined and fully-characterized VMEbus signal timing. VMEbus features include interrupt generation, interrupt handling, slot 1 bus arbitration, A32 D32 transfers for both master and slave operation, high-speed DMA control, block level transfers, bus reset and bus clock drivers.

#### **MIX Bus Interface**

This interface provides a bidirectional 32-bit data path between the Local Bus and the MIX bus. It enables full memory-mapped access to all modules on the MIX bus from the VMEbus, the 68030 and the DMA controller. MIX modules appear as slave devices. An important feature of the interface is the decoupling of one bus from the other, thus allowing each bus to conduct independent memory cycles.

MIX modules with MIX bus master capability may use the Local Bus Interface to access the SRAM, VMEbus and VSBbus with A32 D32 bus master capabilities.

The MIX bus can also be used for dedicated high-speed data transfers between MIX modules. These transfers can be initiated by any MIX module having MIX bus master capability, or by the 68030.

[Continued on next page]

#### **Features**

- Single-slot conversion of standard-size Pentek MIX modules to VME boards

- VMEbus master and slave interface

- MIX bus master and slave interface

- VSBbus master interface in Model 4200A

- Supports system controller functions

- Efficient transfers using DMA controller

- Conserves VMEbus and VSBbus bandwidth

# Block Diagram, Models 4200A, 4201A

# MIX-VME Baseboards/Embedded Controllers

#### **VSBbus Interface**

The VSBbus is a 32-bit data and 32-bit address subsystem bus which utilizes pins on the P2 connector not defined within the VMEbus specification. The Model 4200A includes a VSBbus master interface which can be used by any MIX bus master or by the 68030. The VSBbus is mapped as a region in the address space of the local bus.

This capability can be very useful when a C40 MIX module needs a very large memory store. Since activity on the VSBbus is completely unaffected by VMEbus traffic, a large VSB slave memory can be easily accessed for sustained, high-speed data transfers.

## **Interrupt Processing**

The extensive interrupt handling capability provided by the VIC can be used to create extremely powerful data transfer systems.

For example, interrupts from a half-full FIFO buffer on an A/D converter MIX module can be used to trigger the DMA controller to begin block level transfers from the A/D FIFO to a slave memory on the VMEbus.

To initiate a complex DSP task, a VMEbus interrupt can be directed through the MIX bus to interrupt any MIX coprocessor.

MIX modules can interrupt each other across the MIX bus, as in the case of a SCSI controller module signalling to a coprocessor that it is ready for more data.

#### **Transfer Rates**

Transfer rates depend on the MIX module characteristics, the interface of the other VME board, and the 4200A/4201A processor speed. Below are some measured transfer rates for a 40 MHz 4200A and a typical memory board.

DMA Controller moves data SRAM⇔VME 25 MB/sec MIX⇔VME 12 MB/sec 68030 moves data MIX⇔SRAM 10 MB/sec SRAM⇔VSB 11 MB/sec MIX⇔VSB 8 MB/sec

# **Ethernet Interface**

Option -020 converts a 4200A or 4201A to an Ethernet interface. To implement this option a front panel is attached to the baseboard. Ethernet connectors, one for 10baseT twisted pair using a RJ-11 and a DB 15 AUI are provided, along with two serial ports,

LEDs and a reset button. Since the front panel is needed for Ethernet connection, you cannot nest the first MIX module in the same slot with the baseboard when you have option -020.

## **Specifications**

MIX interface: data and address; bus master and slave operation; bidirectional 32-bit data and address path to local bus

VMEbus interface: bus master and slave, MD32, SD32, MA32, I(1-7); employs VIC/VAC chip set with DMA controller between VMEbus and local bus.

VSB interface (4200A only): bus master, MD32, MA32; PLX chip set

**Processor:** 40 MHz 68030, full memory access to VME, VSB and MIX interfaces

DMA controller: High speed transfers between VMEbus provided by the VIC and VAC chip set; 32-bit data and address transfers, programmable block size, block level transfers supported

**SRAM:** 1MB standard, 4 MB optional; zero-wait-state operation for 68030

Flash memories: 2 x 256 kB; boot for factory firmware to initialize board and support VIC/VAC and DMA controller functions; user for complex DMA routines and standalone applications

Interrupt generation: seven levels of VMEbus with user-defined interrupt vectors supported

Interrupt handling: VIC handles interrupts from seven levels of VMEbus, any MIX modules, VSBbus, two VAC serial ports, status and control interrupts from VAC or interrupts from 68030; also edge/level control, polarity control and user-defined local interrupt priority level (IPL)

**Local Bus address decoding:** VAC decodes address space to allocate memory within SRAM and flash memories, VSB interface and MIX interface.

Accessories: VME front panel with LED, two RS-232 serial ports, and reset button; can be removed after development

**Power:** 1.6 A at +5 V dc; 0.02 A at ±12 V; plus MIX module power requirements **Size:** standard 6U VMEbus board, single slot; board 160 mm (6.3 in.) x 233.5 mm

(9.2 in.)

# **16-channel Signal Processing System**

16-channel data acquisition and signal analysis system with T1/E1 interface fits in just four VMEbus slots. System consists of a 4200A MIX Baseboard, a 4257 Dual C40 Coprocessor, a 4259 T1/E1 Transceiver and a Model 4252 16-channel A/D and D/A Converter.

#### **Ordering Information**

Model Description

4200A MIX-VME Baseboard,

Master/Slave with VSB

Interface, 1 MB SRAM,

40 MHz processor

4201A MIX-VME Baseboard,

Master/Slave without

VSB Interface, 1 MB

SRAM, 40 MHz

processor

Options:

-004 4 MB SRAM, both

models

-020 Ethernet interface