# **General Information**

Designed for applications requiring extremely high-speed signal processing and data transfers, the Model 4292 features four Texas Instruments TMS320C6203 DSPs. Operating at 300 MHz, they deliver a combined peak processing capability of 9600 MIPS.

### TMS320C6203 DSP

As a member of the C6000 family, the C6203 utilizes TI's 0.15 micron process which delivers 896 kB of on-chip SRAM, 512 kB for data and 384 kB for program, eliminating the need for external memory access in many applications.

The VLIW engine executes up to eight instructions in a single 300 MHz clock

cycle, delivering up to 2400 MIPS. The powerful DMA controller transfers data to peripherals over dual 32-bit external data busses at rates as high as 600 MB/sec. Two serial ports easily support popular telecom interfaces.

# **Overall Circuit Description**

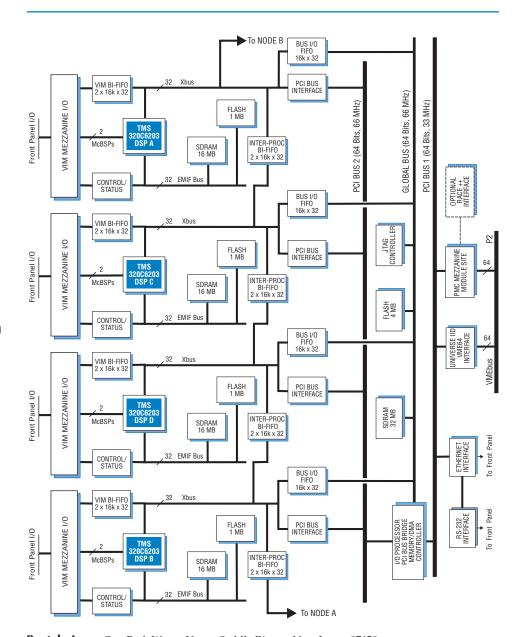

Four identical processor nodes contain interface and memory resources ideally matching the I/O capabilities of the C6203 to high-performance system components.

Each node includes local memory, a dedicated high-speed mezzanine interface, interprocessor links, a dedicated bus I/O channel, and connections to powerful shared board resources. >

### Features

- Four TMS320C6203 DSPs

- 9600 MIPS peak processing power

- High-performance PMC and VIM mezzanine module sites

- Four 300 MB/sec interprocessor BI-FIFOs

- Four 300 MB/sec Bus I/O FIFOs

- Four 8 MB or 16 MB SDRAMs, 600 MB/sec transfer rate

- 32 MB of shared global SDRAM with 528 MB/sec peak transfer rate

- VME64 master/slave interface

- Optional RACE++ interface with transfer rate to 267 MB/sec

Pentek, Inc. One Park Way

Upper Saddle River

New Jersey 07458

Tel: 201.818.5900

Fax: 201.818.5904

Email: info@pentek.com

#### **Support Software**

Pentek's **SwiftNet** supports a network of distributed VMEbus systems and allows the developer to run development tools on the host, while maintaining remote access to the VMEbus system.

Pentek's **ReadyFlow** Board Support Libraries reduce development time by providing C-language callable functions for hardware initialization, control and operation of board resources.

TI's **Code Composer Studio** provides a comprehensive set of tools for software development including an optimizing C Compiler, an interactive debugger, the DSP/BIOS operating system and an assortment of profiling and optimizing tools.

### **Ordering Information**

| Model | Description          |

|-------|----------------------|

| 4292  | Quad C6203 Processor |

|       | PMC/VIM - VME        |

#### Options:

| -005                     | RACE++ Interface                                   |

|--------------------------|----------------------------------------------------|

| -320                     | 16 kB VIM and IP<br>BI-FIFO, 16 kB Bus I/O<br>FIFO |

| -340                     | 16 MB local SDRAM<br>(8 MB std.)                   |

| * Contact Pentek for PMC |                                                    |

| compatibility            |                                                    |

PENTEK

### ► VIM Mezzanine

Each processor is equipped with its own VIM (Velocity Interface Mezzanine) connector, providing three types of interfaces. A high-speed synchronous bidirectional FIFO (BI-FIFO) buffers 32-bit parallel data transfers between the mezzanine and the C6203's expansion (EXP) bus at rates up to 300 MB/sec. Two of the C6203's synchronous serial ports are also brought to the mezzanine connector. The External Memory Interface (EMIF) bus of the C6203 provides memory-mapped control and status functions to the mezzanine circuitry.

### **Local Memory**

Two types of local memory resources are provided for each C6203: a 16 MB SDRAM operating with single-wait state access, and a nonvolatile 1 MB flash memory for initialization, self-test and boot code.

#### **Interprocessor BI-FIFOs**

Because the C6203 includes no inter-processor communication links, the Model 4292 features four BI-FIFOs joining the EXP busses of each adjacent C6203 in a ring structure. Each C6203 can send and receive interprocessor data blocks at 300 MB/sec without having to arbitrate for a shared resource.

## **Bus I/O FIFOs**

By using a private bus I/O FIFO, each processor can transfer blocks of data to global resources including the VMEbus, global SDRAM, the PMC site, and the optional RACE++ interface. These FIFOs are extremely effective in decoupling the C6203's from these resources and eliminating wait cycles while allowing 300 MB/sec block transfers.

## **PCI Master Interface**

Each C6203 can master the Primary PCI bus for read/write access to RACEway, VMEbus, global SDRAM and the PMC site.

### **Global SDRAM**

Serving as a convenient shared resource for staging data, the 32 MB global SDRAM is accessible from all four processors, the VMEbus, the PMC site and the optional RACE++ interface.

### Ethernet/RS-232 Interface

Front Panel 100 BaseT and RS-232 interfaces provide a gateway for debugging during development, and data transfers at run time.

### **PMC Site**

In addition to accommodating Pentek's broad range of VIM I/O peripherals, Model 4292 incorporates a PCI Mezzanine Card (PMC) module site, which accepts industry-standard modules for a wide variety of interface and communication functions. The PMC module is accessible from all four C6203's and from the VMEbus.

## **Peripheral I/O**

Model 4292 may be equipped with two VIM-2 modules, either identical or providing different functions; one VIM-4 module; or one VIM-2 module in the upper position and one PMC module in the lower position. VIM I/O modules include narrowband and wideband digital receivers and upconverters, A/D and D/A converters, FPDP interfaces and many more.

### VME64 Interface

All four processors can master the VMEbus using the industry standard Universe II VME64 interface chip. As a VMEbus slave, Model 4292 presents the global SDRAM, the four Bus I/O BI-FIFOs, and the PMC site as memory mapped resources.

### **Optional RACE++ Interface**

Delivering up to 267 MB/sec between VME boards, the optional RACE++ interface occupies the PMC connector and allows all four processors to send and receive RACEway packets using the bus I/O FIFOs as private data buffers. The RACE++ option maintains the board's one VMEbus slot configuration with two VIM modules.

### **Specifications**

Processor Node Resources: 4 total Processor: TMS320C6203, 300 MHz clock SDRAM: 2M x 32; 4M x 32 optional FLASH: 1M x 8 Mezzanine: VIM site Mezzanine and Interprocessor BI-FIFO: 2 x 1k x 32; 2 x 16k x 32 optional Bus I/O FIFO: 1k x 32; 16k x 32 optional Shared Global Resources: Global SDRAM: 4M x 64

FLASH: 4M x 8

VME64 Interface: Tundra Universe II master/slave, slot 1 controller PMC Module Site: 64 bit, 33 MHz, 5 V Front Panel Interfaces: 100 BaseT, RS-232 RACE++ Interface: optional

Size: standard 6U VMEbus board, single slot; board 160 mm (6.3 in.) x 233.5 mm (9.2 in.), panel 0.8 in. wide