## PRODUCT CATALOG

## **Company Profile**

Founded in 1986, Pentek has become the premier source for high-speed real-time recording systems, DSP (Digital Signal Processing), SDR (Software-Defined Radio), and data acquisition products. Our customers enjoy our ISO 9001 SGS certification and the performance and flexibility afforded by our board- and system-level commercial and ruggedized product lines and our world-class applications support.

Pentek is the leading board and system manufacturer offering COTS and ruggedized products in formats such as VPX, PMC/XMC, PCI Express, AMC, FMC, CompactPCI, and PCI, featuring the latest Xilinx Virtex and Kintex FPGAs.

Pentek's data acquisition line is extensive and includes A/Ds, D/As, Digital Receivers/ Transmitters, Digital I/O, Analog RF downconverters, High-speed recorders, Development systems and more.

No other embedded vendor can provide such seasoned, in-depth technical expertise in data acquisition, digital signal processing and software-defined radio.

## **Mission Statement**

Pentek's mission is to provide the embedded community with leading edge board- and system-level solutions for the most demanding requirements in data acquisition, digital signal processing and software radio applications through excellence and innovation.

## **Pentek Strategies**

We support an aggressive new product development cycle to meet market demands as we design the next generation of embedded products.

We consistently invest more than 15% of revenues in product development, engineering and applications support.

We will help you solve the most challenging DSP problems through our dedicated staff of systems engineers who are trained to provide the answers to your hardware, software or applications questions.

We recognize today's time-to-market pressures and budget constraints on development resources and we offer low-risk, easy-to-use embedded solutions.

## **Product Overview**

You can select from the industry's most extensive line of advanced analog and digital I/O products, along with exclusive development tools that help you create a custom system. Many of these products include Xilinx Virtex or Kintex FPGAs for customized processing.

#### **High-Speed Real-Time Recording Systems**

- Economical alternatives to in-house development

- Fully tested and ready to run right out-of-the-box

- Easy to use with full-featured software installed

#### **Processor Engines**

Xilinx Virtex and Kintex FPGAs

#### **Data Acquisition**

- Single or multichannel A/Ds and D/As

- Sampling rates to 3.6 GHz

- Resolution to 24 bits

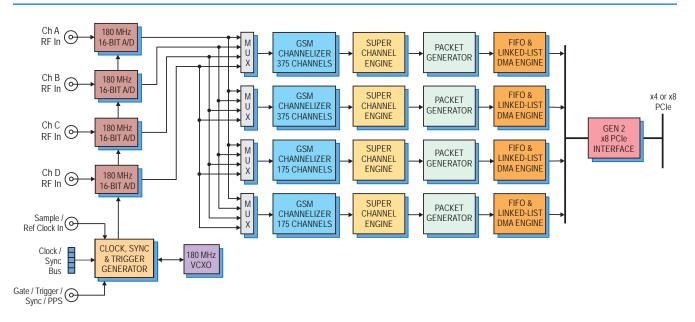

## **Software Radio**

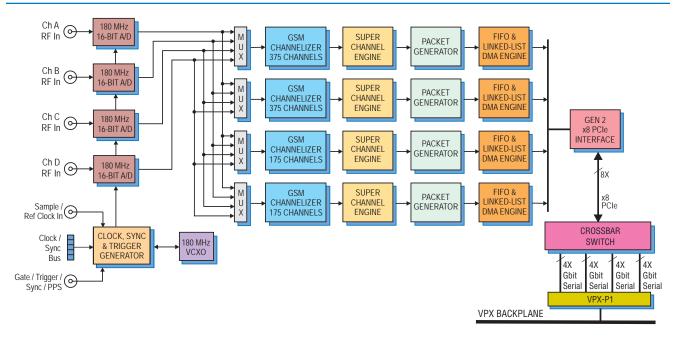

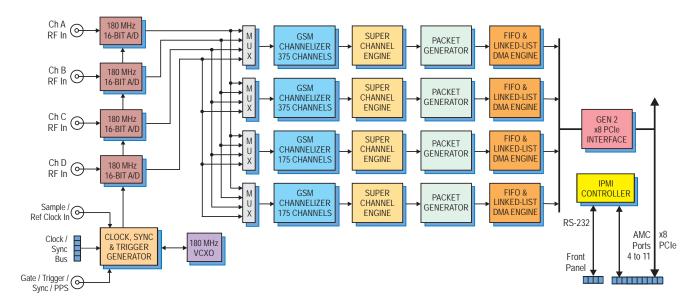

- Up to 1100 channels per slot

- Narrow-, wide- and multi-band versions

- Digital downconverters and upconverters

- Analog downconverters

- Development systems

For more information about us, please visit: http://pentek.com/about/about.cfm?HID2=TM

Pentek's 88,000 sq. ft. facility in Upper Saddle River, NJ

"Pentek takes pride in listening to its customers and creating new products to meet their needs. We promise an atmosphere of freedom and creativity among our engineers, so they can design industry-leading products to satisfy the most demanding applications. This has been the key to our success through the years."

Rodger Hosking, Vice President and Co-founder

## PRODUCT CATALOG CONTENTS

## RADAR & SDR I/O

RADAR & SDR I/O - PMC/XMC

RADAR & SDR I/O - 3U & 6U CompactPCI

RADAR & SDR I/O - x8 PCI Express

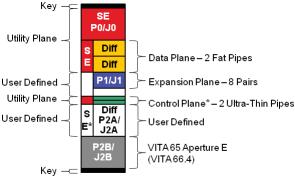

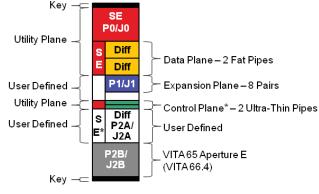

RADAR & SDR I/O - 3U VPX - FORMAT 1

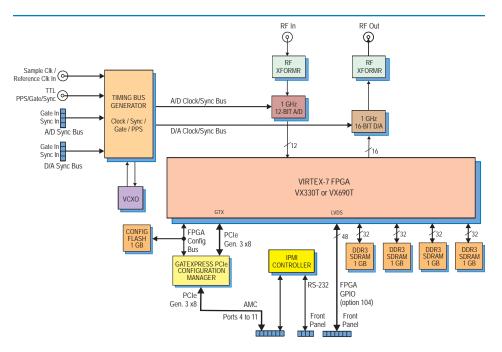

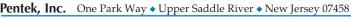

RADAR & SDR I/O - AMC

RADAR & SDR I/O - 3U VPX - FORMAT 2

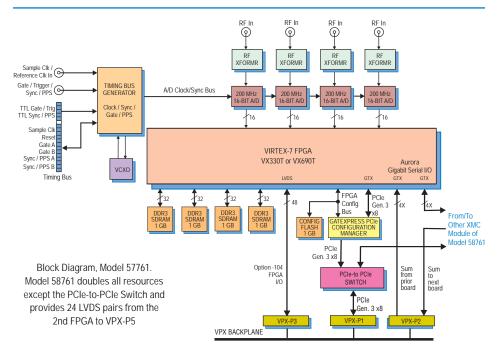

RADAR & SDR I/O - 6U VPX

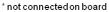

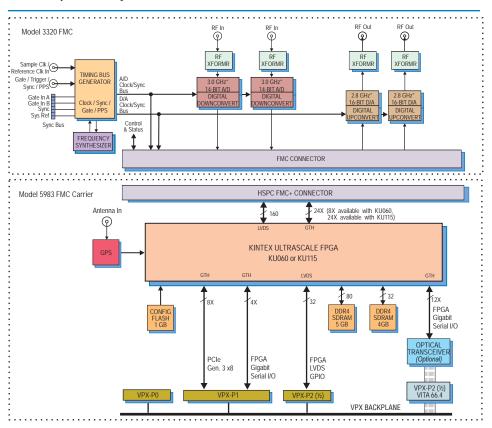

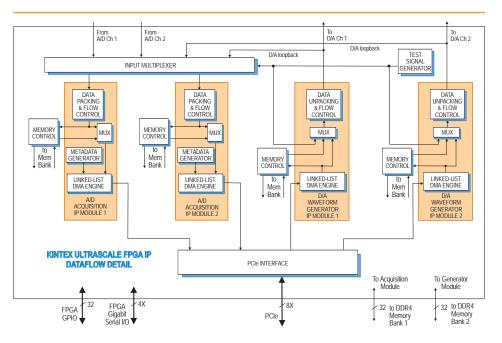

RADAR & SDR I/O - FMC

ANALOG & DIGITAL I/O

HIGH-SPEED RECORDING SYSTEMS

**CLOCK & SYNC GENERATORS**

SOFTWARE & FPGA TOOLS

# RADAR & SDR I/O - PMC/XMC

| MODEL               | DESCRIPTION                                                                             |

|---------------------|-----------------------------------------------------------------------------------------|

| Cobalt 71620        | 3-Channel 200 MHz A/D, 2-Channel 800 MHz D/A, Virtex-6 FPGA - XMC                       |

| Cobalt 71621        | 3-Channel 200 MHz A/D with DDC, DUC, 2-Channel 800 MHz D/A, Virtex-6 FPGA - XMC         |

| Cobalt 71624        | Dual-Channel, 34-Signal Adaptive IF Relay - XMC                                         |

| Cobalt 71630        | 1 GHz A/D and D/A, Virtex-6 FPGA - XMC                                                  |

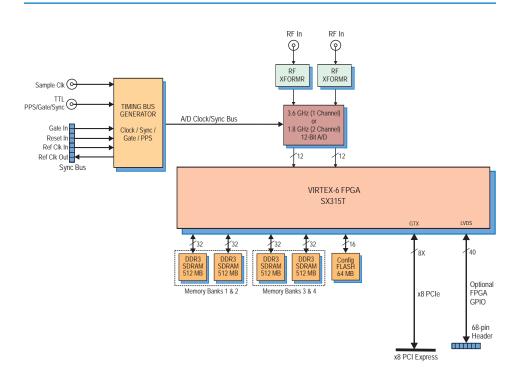

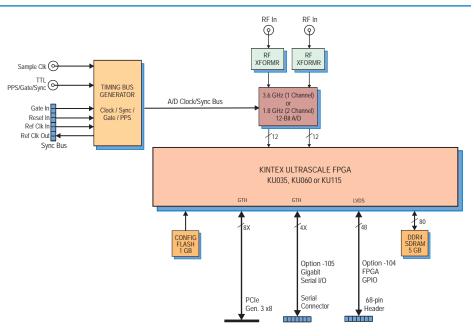

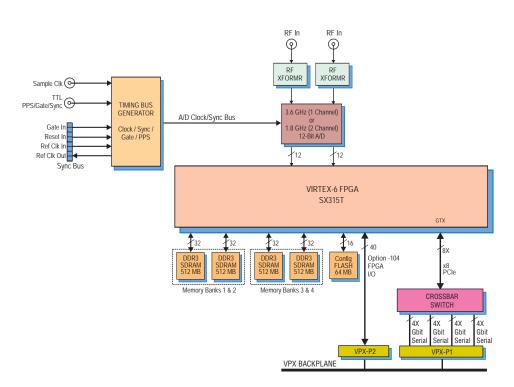

| Cobalt 71640        | 1-Channel 3.6 GHz or 2-Channel 1.8 GHz 12-bit A/D, Virtex-6 FPGA - XMC                  |

| Cobalt 71641        | 1-Channel 3.6 GHz or 2-Channel 1.8 GHz 12-bit A/D, Wideband DDC, Virtex-6 FPGA - XMC    |

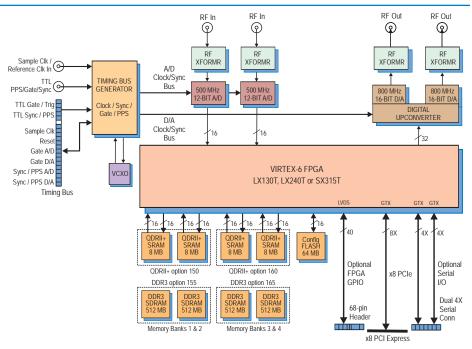

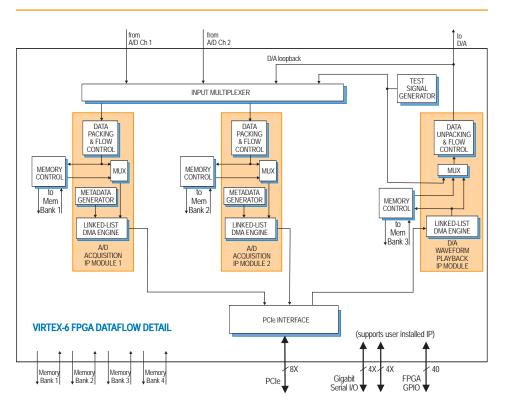

| Cobalt 71650        | Two 500 MHz A/Ds, DUC, 800 MHz D/As, Virtex-6 FPGA - XMC                                |

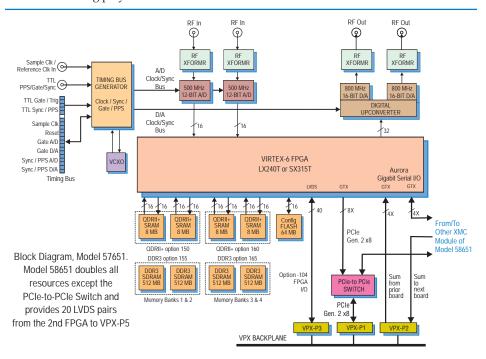

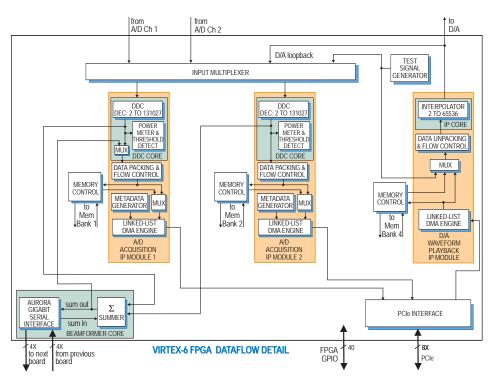

| Cobalt 71651        | 2-Chan 500 MHz A/D with DDC, DUC with 2-Chan 800 MHz D/A, Virtex-6 FPGA - XMC           |

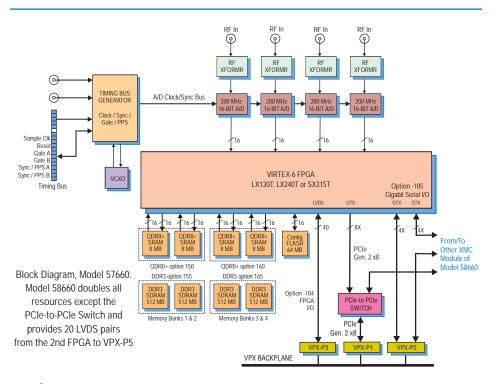

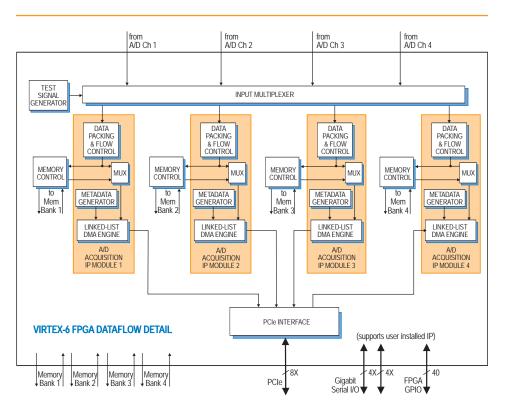

| Cobalt 71660        | 4-Channel 200 MHz, 16-bit A/D, Virtex-6 FPGA - XMC                                      |

| Cobalt 71661        | 4-Channel 200 MHz A/D with DDCs and Virtex-6 FPGA - XMC                                 |

| Cobalt 71662        | 4-Channel 200 MHz A/D with 32-Channel DDC and Virtex-6 FPGA - XMC                       |

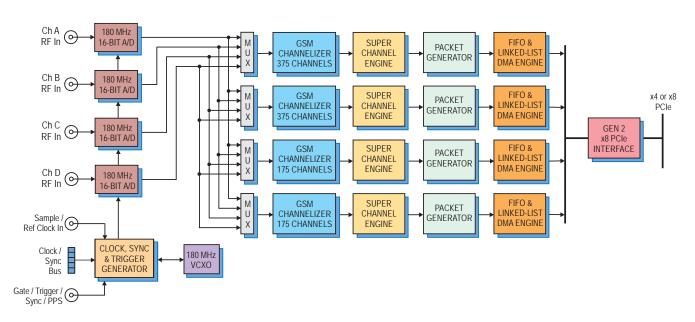

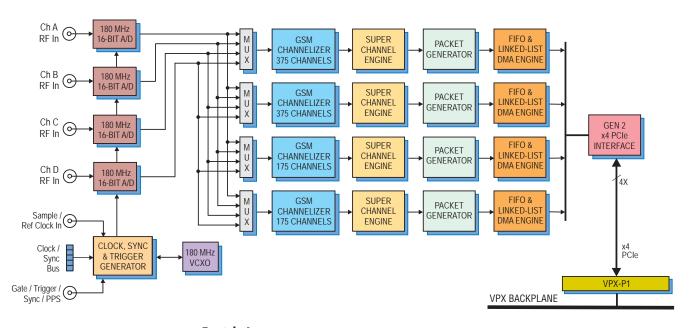

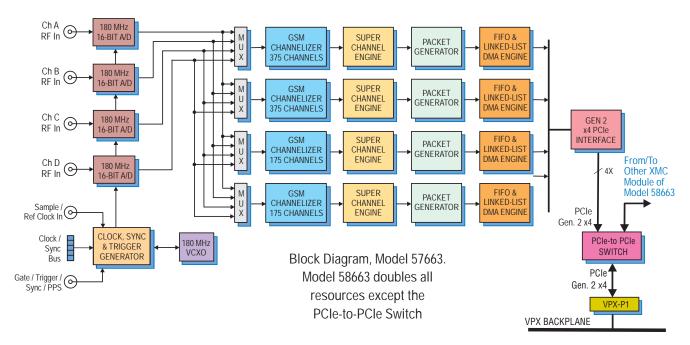

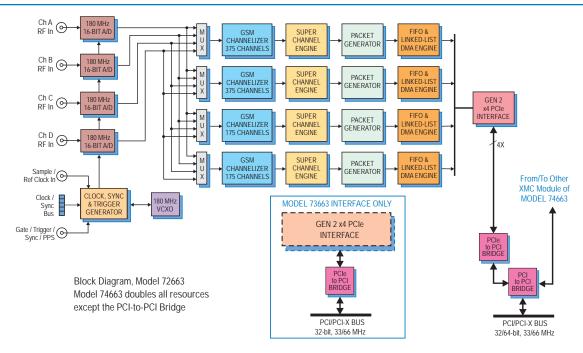

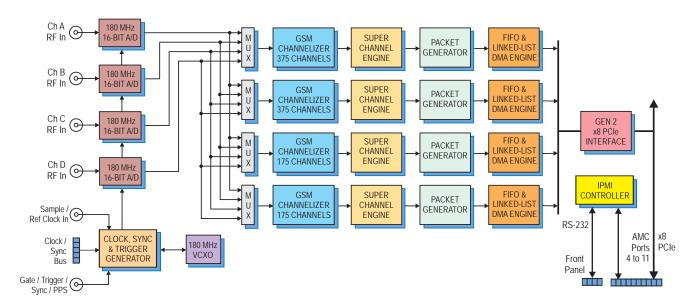

| Cobalt 71663        | 1100-Channel GSM Channelizer with Quad A/D - XMC                                        |

| Cobalt 71664        | 4-Channel 200 MHz A/D with DDCs, VITA-49, Virtex-6 FPGA - XMC                           |

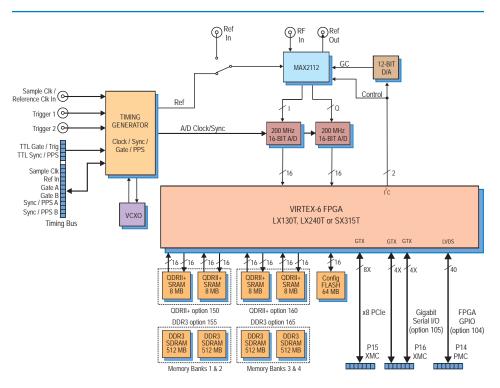

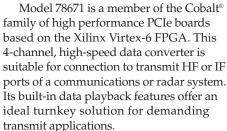

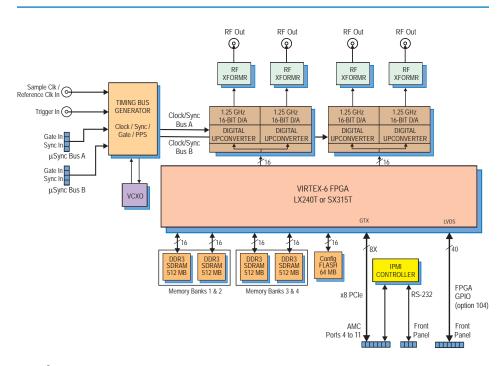

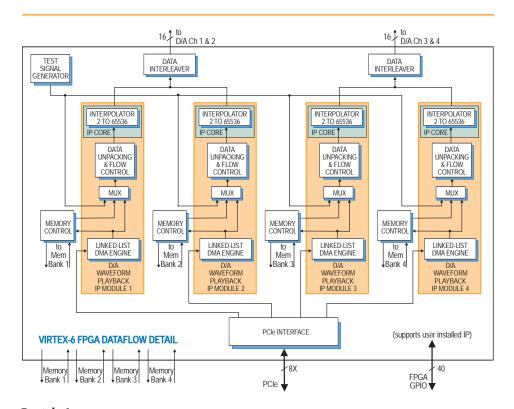

| Cobalt 71670        | 4-Channel 1.25 GHz D/A with DUC, Virtex-6 FPGA - XMC                                    |

| <u>Cobalt 71671</u> | 4-Channel 1.25 GHz D/A with DUC, Extended Interpolation and Virtex-6 FPGA - XMC         |

| Cobalt 71690        | L-Band RF Tuner, 2-Channel 200 MHz A/D, Virtex-6 FPGA - XMC                             |

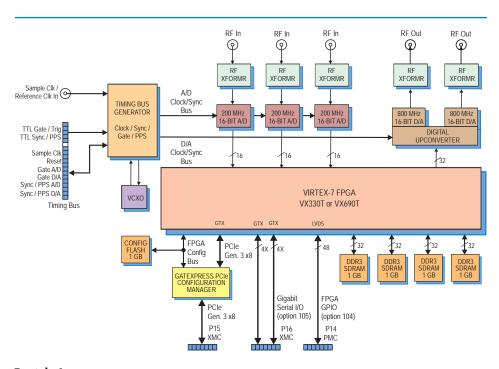

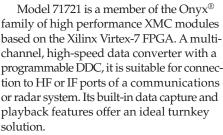

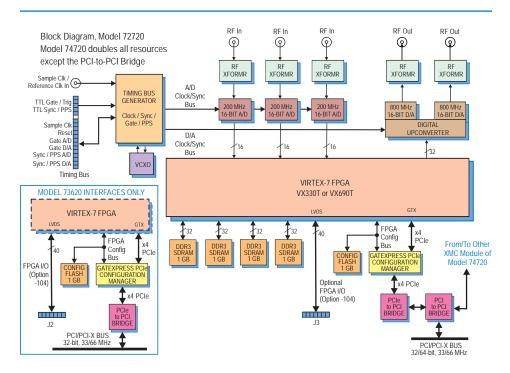

| Onyx 71720          | 3-Channel 200 MHz A/D, 2-Channel 800 MHz D/A, Virtex-7 FPGA - XMC                       |

| Onyx 71721          | 3-Channel 200 MHz A/D with DDC, DUC, 2-Channel 800 MHz D/A, Virtex-7 FPGA - XMC         |

| Onyx 71730          | 1 GHz A/D and D/A, Virtex-7 FPGA - XMC                                                  |

| Onyx 71741          | 1-Ch. 3.6 GHz or 2-Ch. 1.8 GHz, 12-bit A/D, w/ Wideband DDC, Virtex-7 FPGA - XMC        |

| Onyx 71751          | 2-Channel 500 MHz A/D, DDC, DUC, 2-Channel 800 MHz D/A, Virtex-7 FPGA - XMC             |

| <u>Onyx 71760</u>   | 4-Channel 200 MHz, 16-bit A/D, Virtex-7 FPGA - XMC                                      |

| Onyx 71761          | 4-Channel 200 MHz, 16-bit A/D with DDCs and Virtex-7 FPGA - XMC                         |

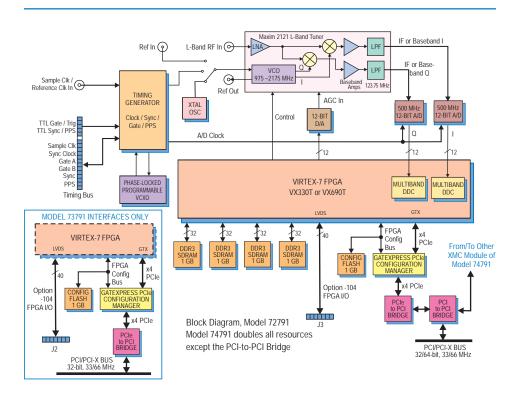

| Onyx 71791          | L-Band RF Tuner, 2-Channel 500 MHz A/D, Virtex-7 FPGA - XMC                             |

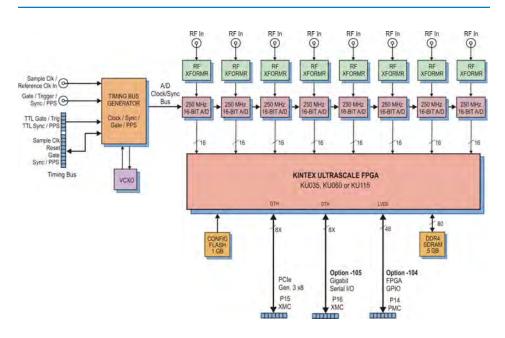

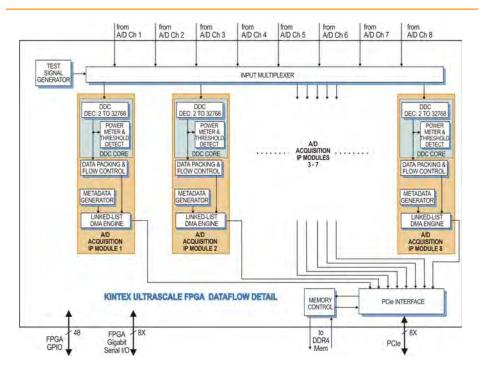

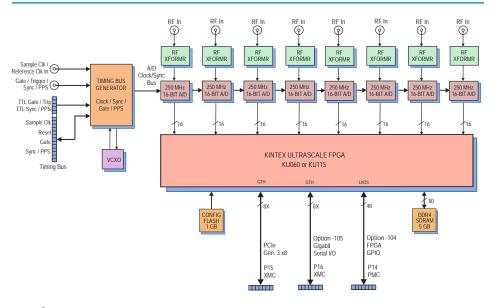

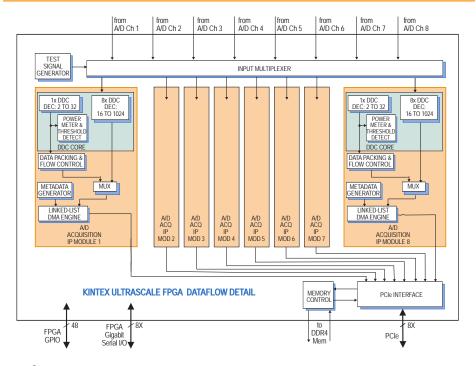

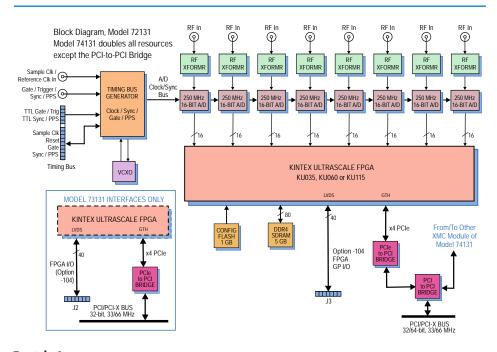

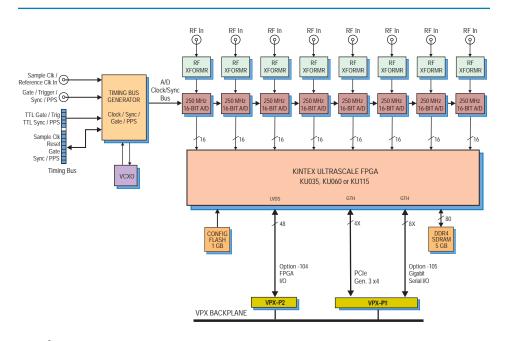

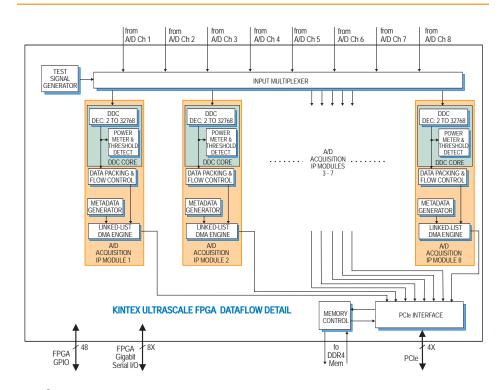

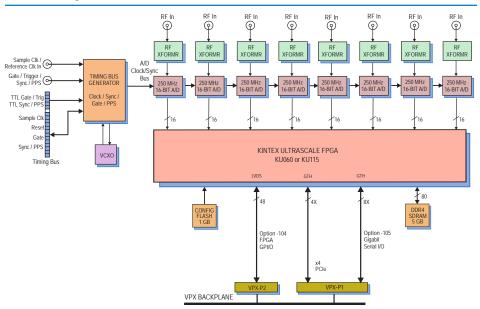

| <u>Jade 71131</u>   | 8-Channel 250 MHz A/D with DDCs and Kintex UltraScale FPGA - XMC                        |

| <u>Jade 71132</u>   | 8-Channel 250 MHz A/D with Multiband DDCs and Kintex UltraScale FPGA - XMC              |

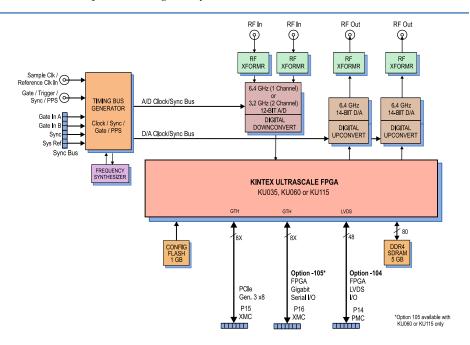

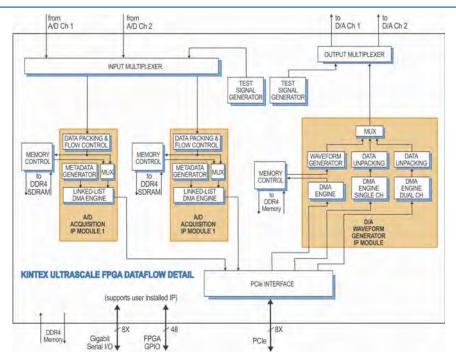

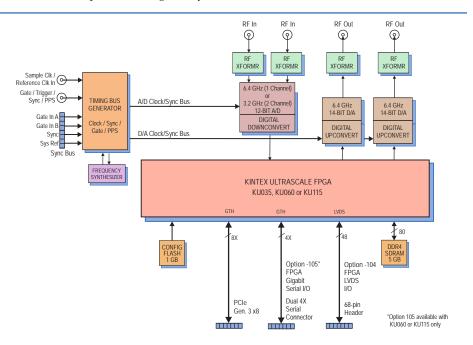

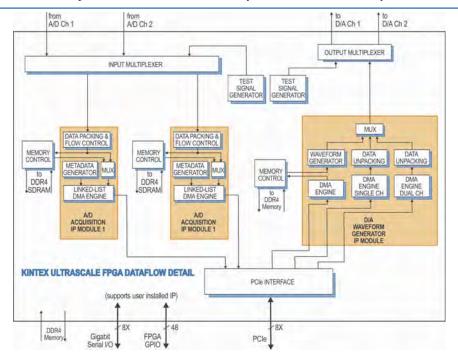

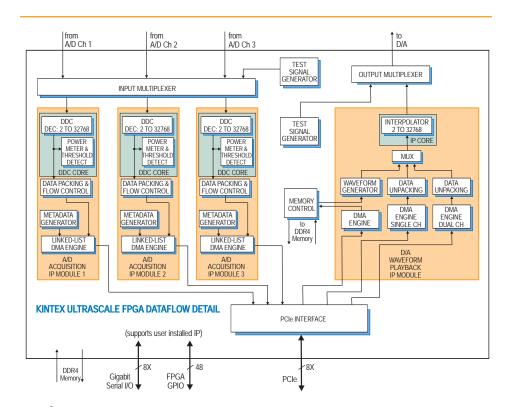

| <u>Jade 71141</u>   | 1-Ch. 6.4 GHz or 2-Ch. 3.2 GHz A/D, 2-Ch. 6.4 GHz D/A, and Kintex UltraScale FPGA - XMC |

| <u>Jade 71821</u>   | 3-Channel 200 MHz A/D, DDC, DUC 2_Channel 800 MHz D/A, Kintex UltraScale FPGA - XMC     |

| <u>Jade 71841</u>   | 1-Ch. 3.6 GHz or 2-Ch. 1.8 GHz, 12-bit A/D, Wideband DDC, Kintex UltraScale FPGA - XMC  |

| <u>Jade 71851</u>   | 2-Ch. 500 MHz A/D, DDC, DUC, 2-Ch. 800 MHz D/A, Kintex UltraScale FPGA - XMC            |

| <u>Jade 71861</u>   | 4-Channel 200 MHz A/D with DDcs and Kintex UltraScale FPGA - XMC                        |

| <u>Jade 71862</u>   | 4-Channel 200 MHz A/D with Multiband DDCs, Kintex Ultrascale FPGA - XMC                 |

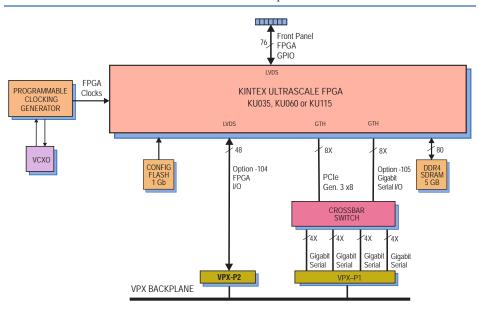

| <u>Jade 71800</u>   | Kintex UltraScale FPGA Coprocessor - XMC                                                |

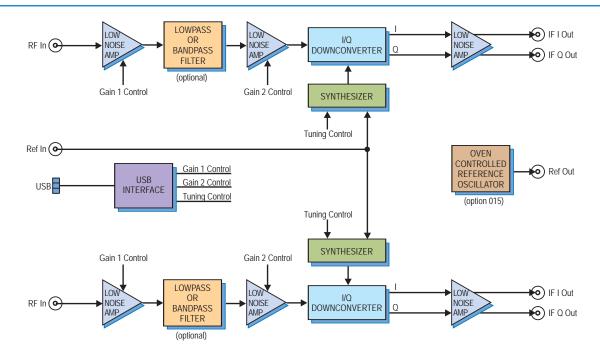

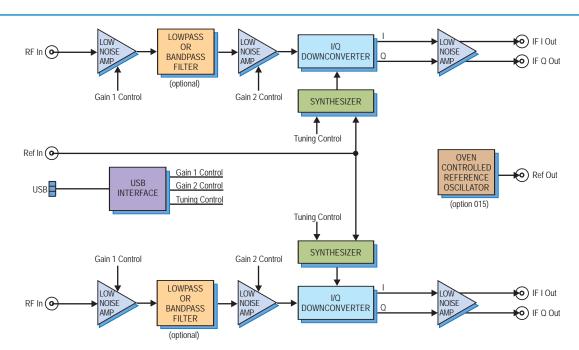

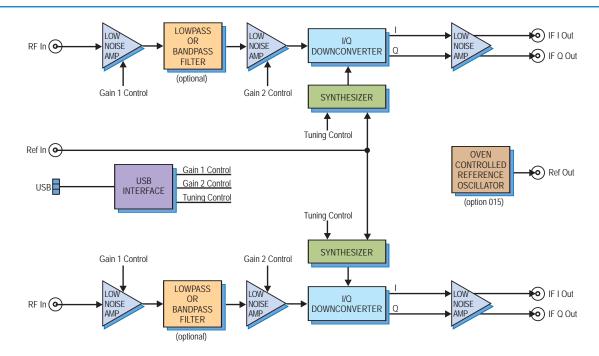

| <u>Bandit 7120</u>  | 2-Channel Analog RF Wideband Downconverter - PMC/XMC                                    |

| <u>8266</u>         | PC Development System for PCIe Cobalt, Onyx, Jade and Flexor Boards                     |

|                     | <u>Customer Information</u>                                                             |

RADAR & SDR I/O - CompactPCI

Click Here for the PRODUCT SELECTOR

RADAR & SDR I/O - x8 PCI Express

RADAR & SDR I/O - 3U VPX - FORMAT 1

RADAR & SDR I/O - AMC

RADAR & SDR I/O - 3U VPX - FORMAT 2

RADAR & SDR I/O - 6U VPX

RADAR & SDR I/O - FMC

www.pentek.com

Last updated: March 2018

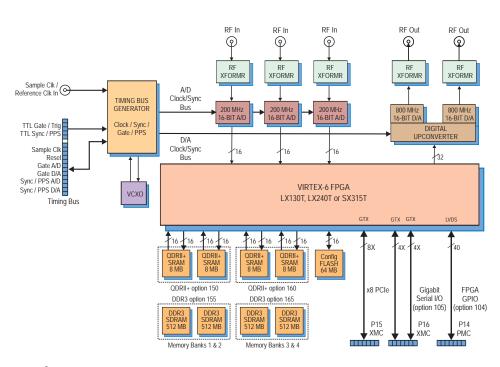

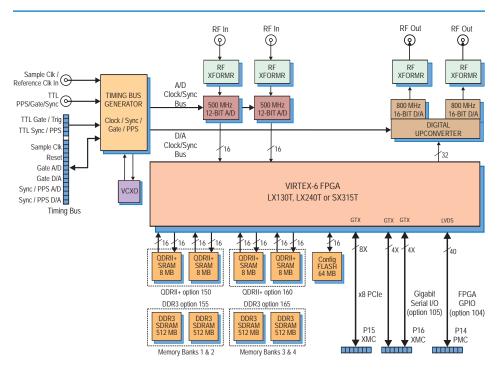

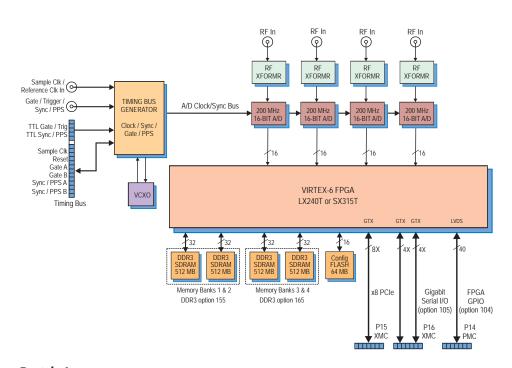

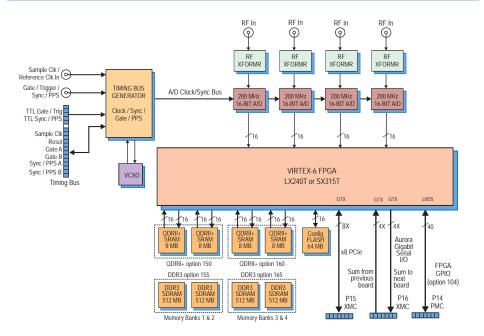

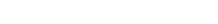

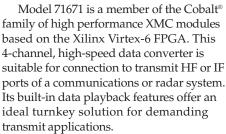

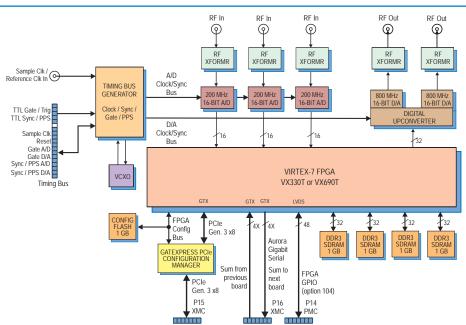

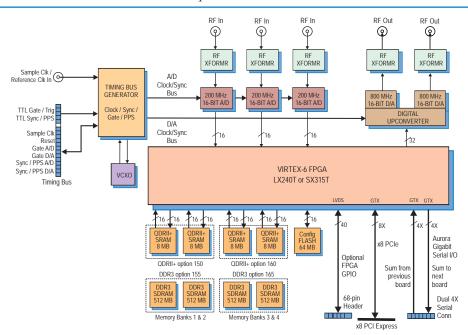

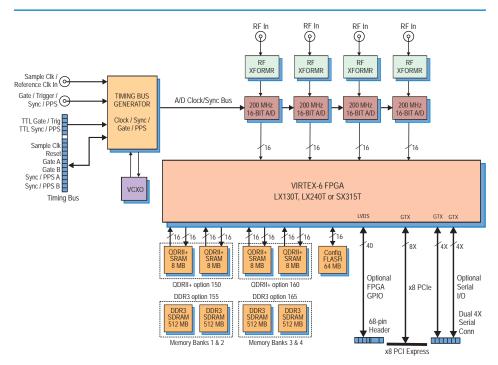

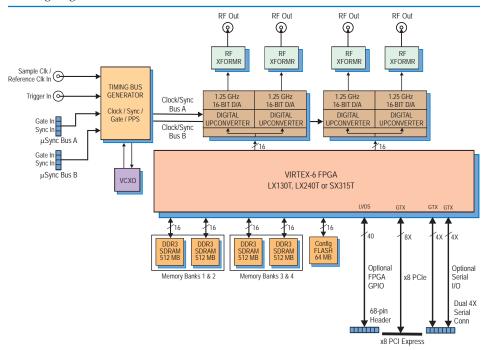

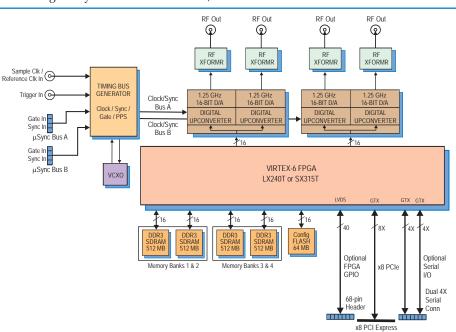

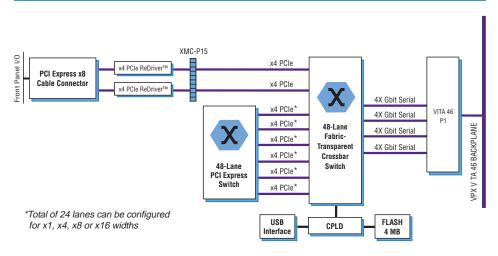

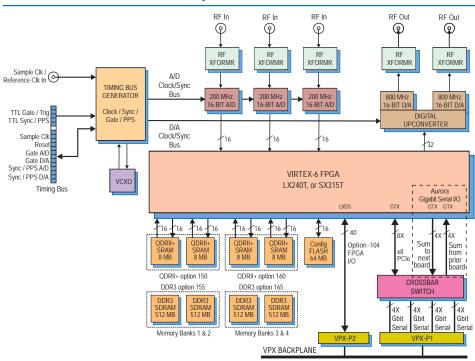

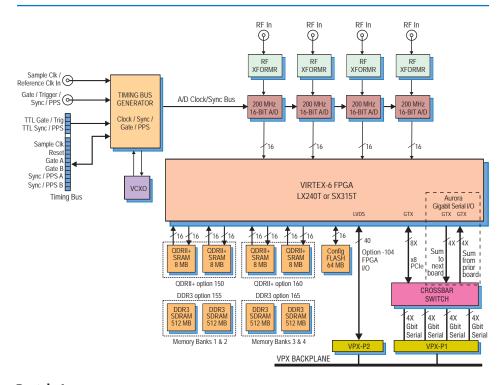

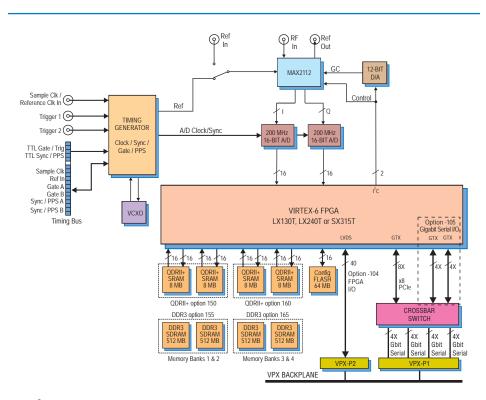

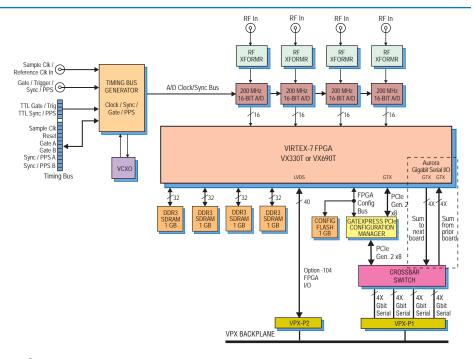

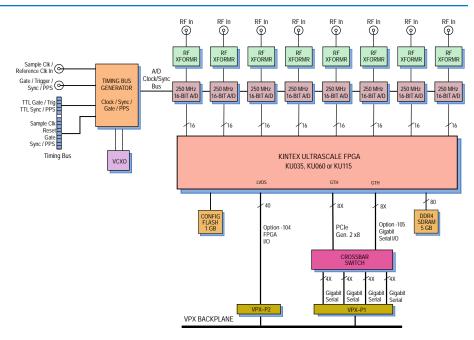

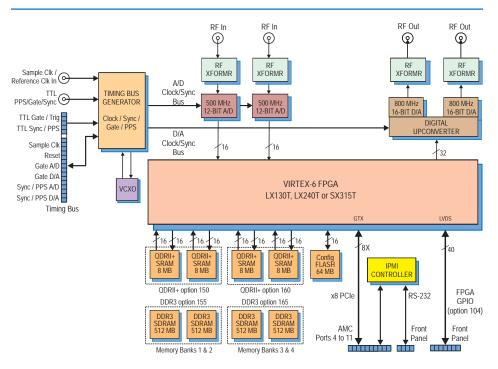

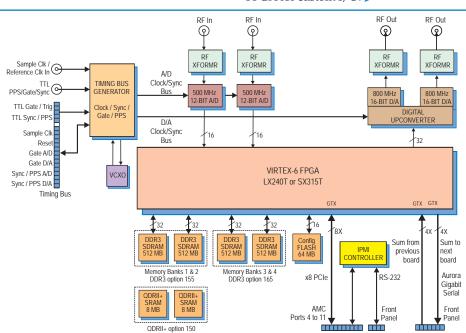

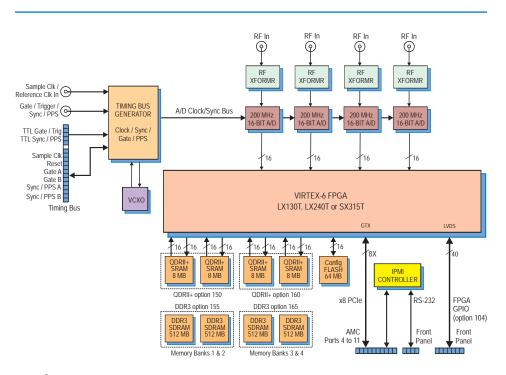

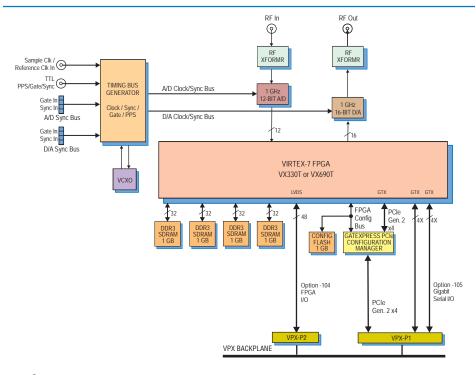

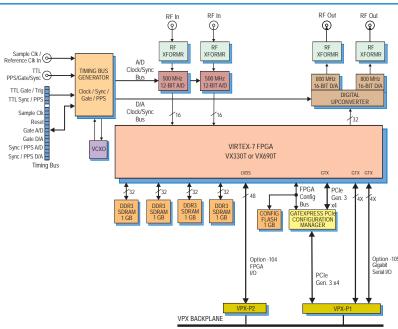

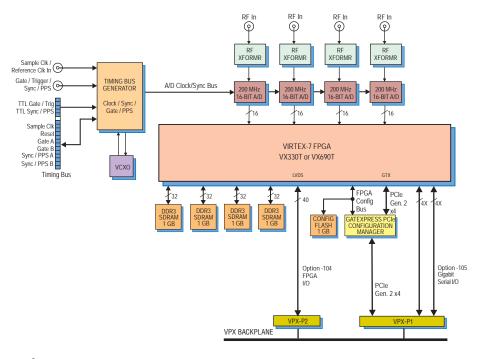

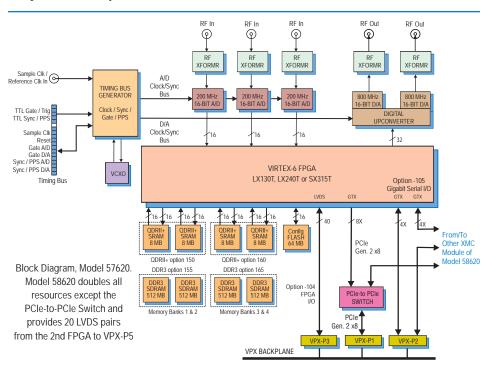

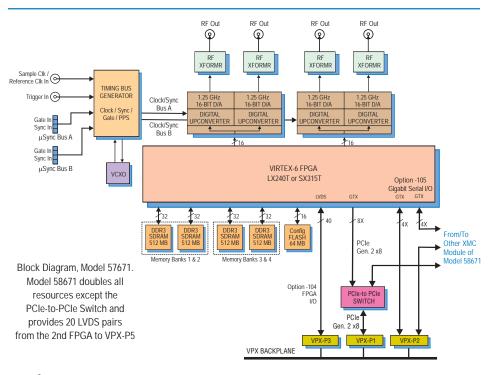

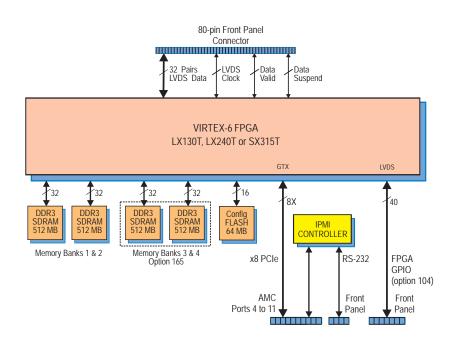

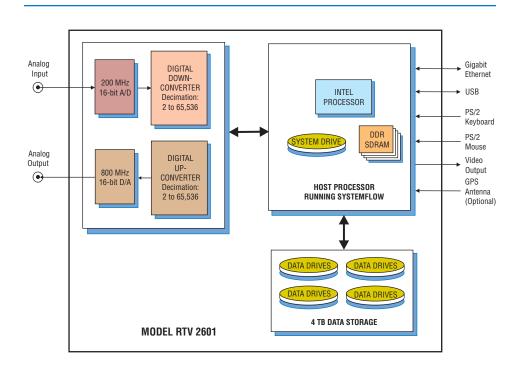

#### **Features**

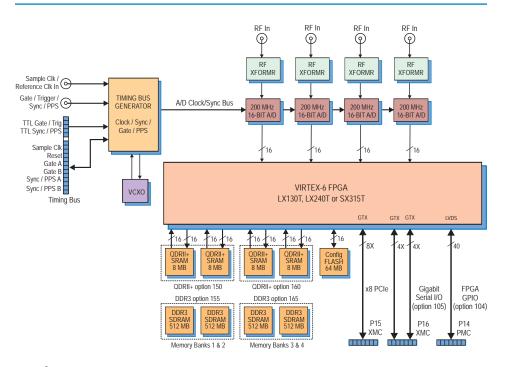

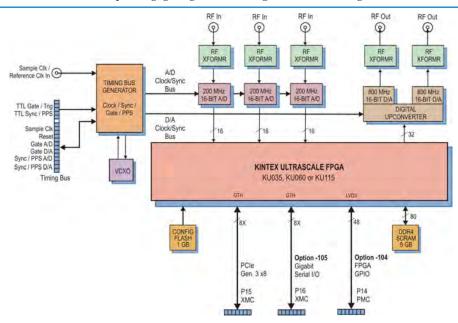

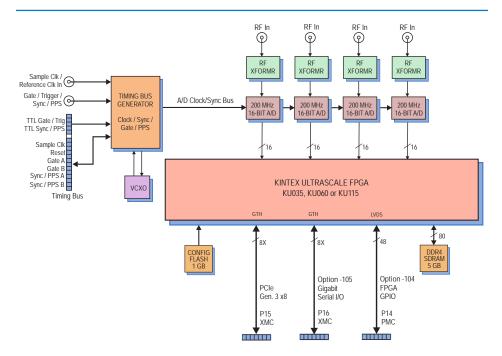

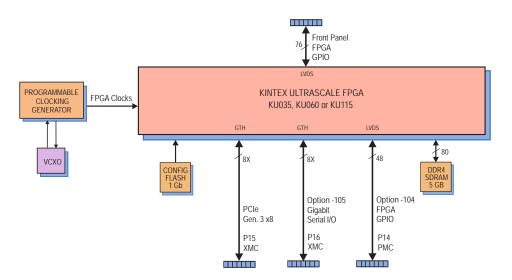

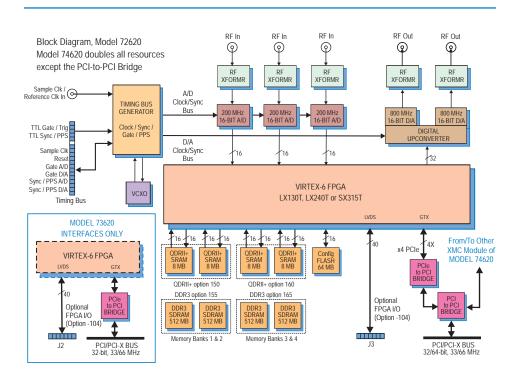

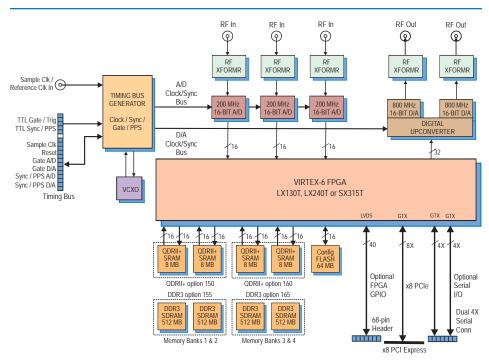

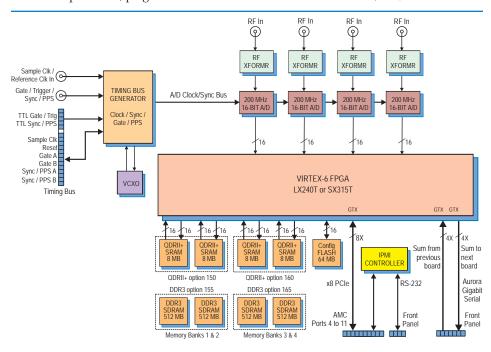

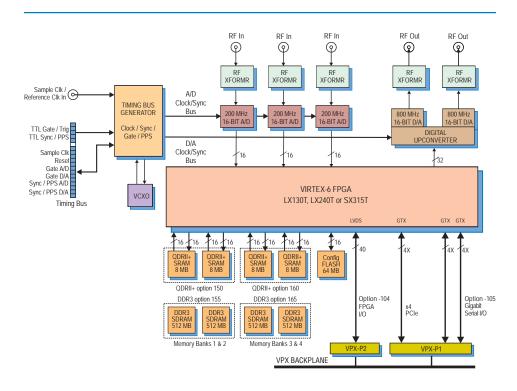

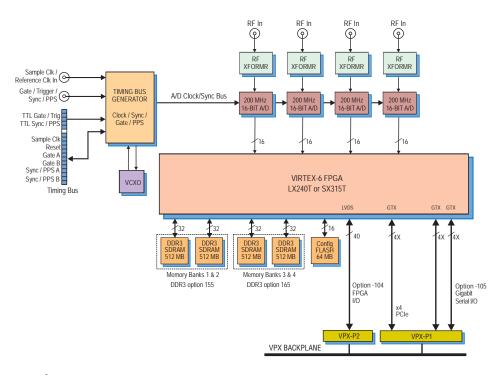

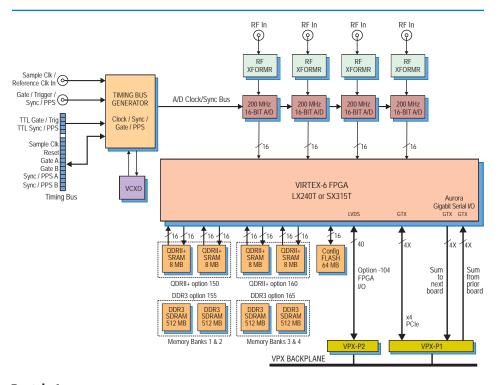

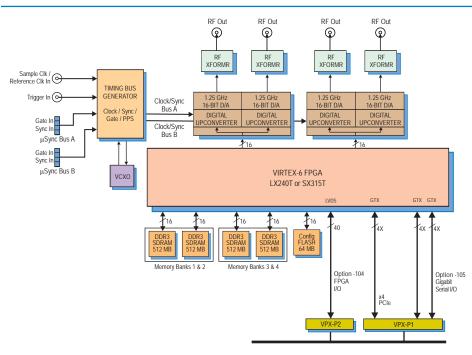

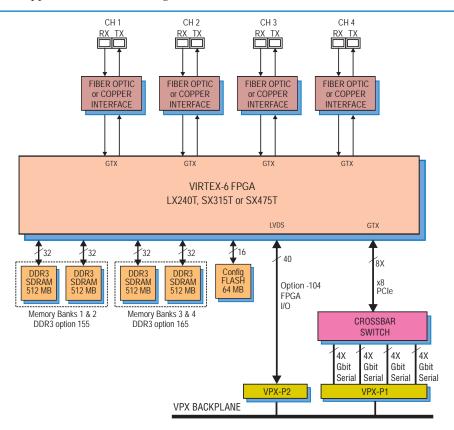

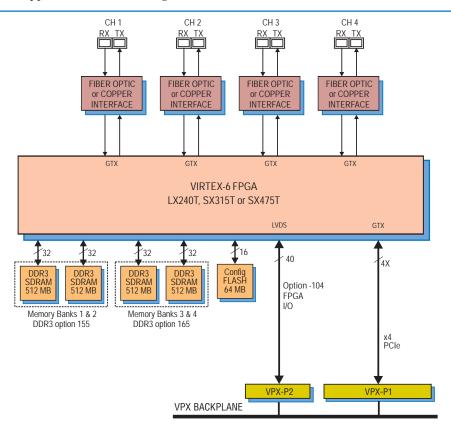

- Complete radar and software radio interface solution

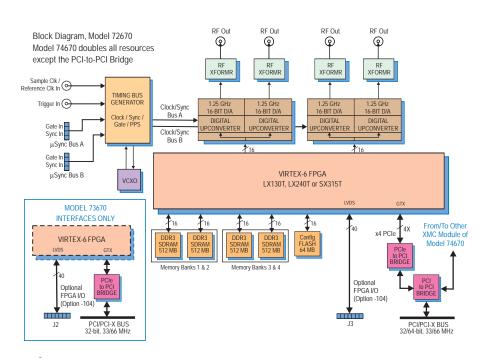

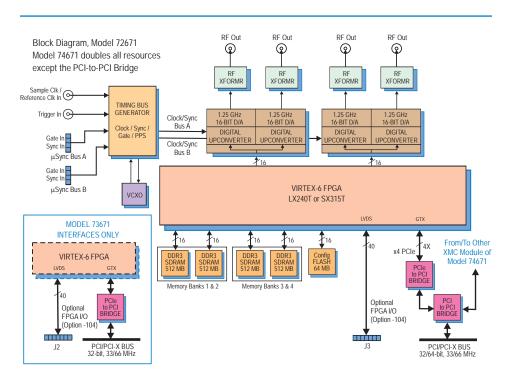

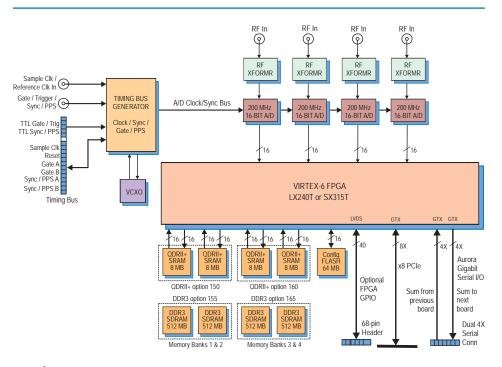

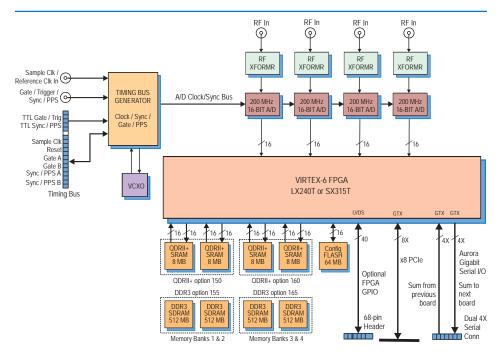

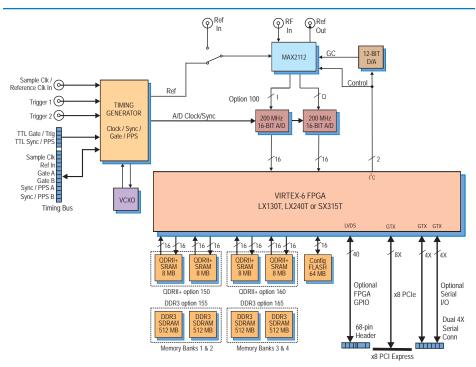

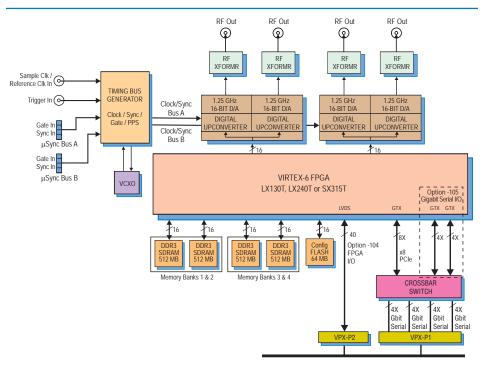

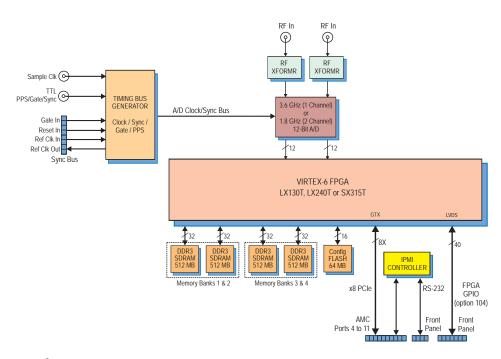

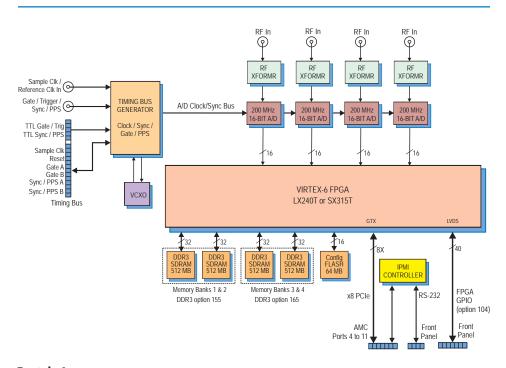

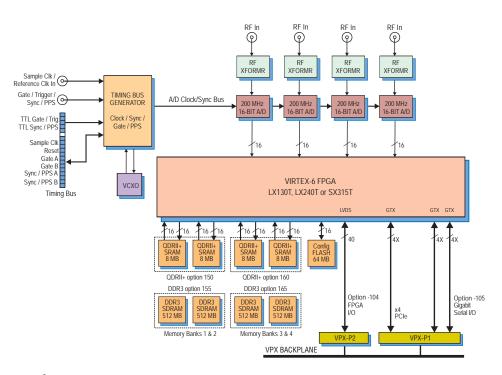

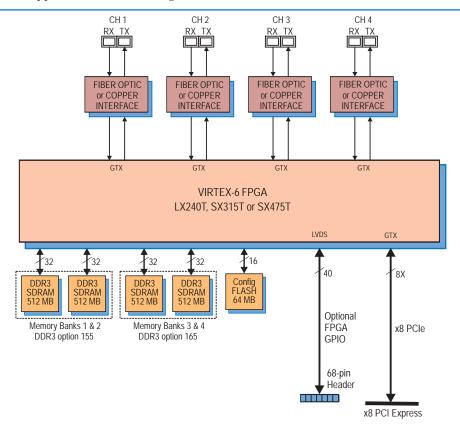

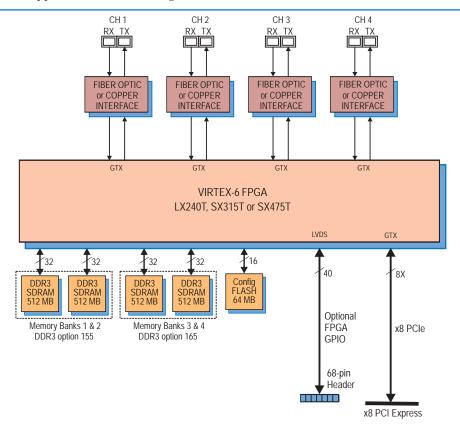

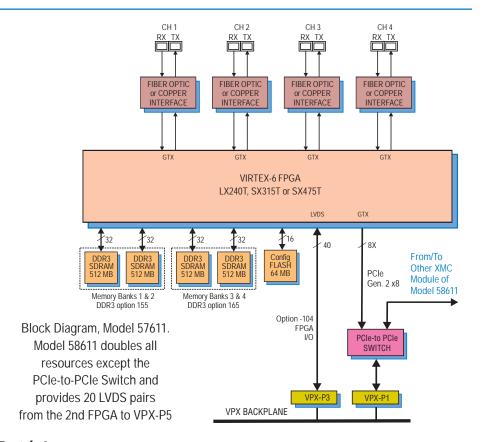

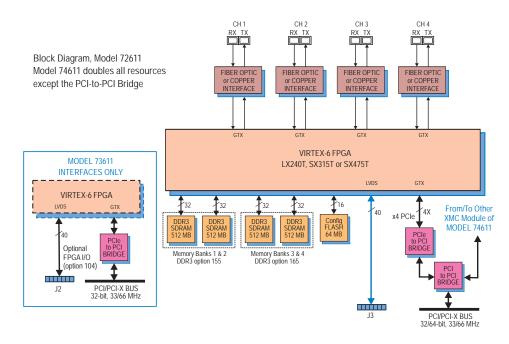

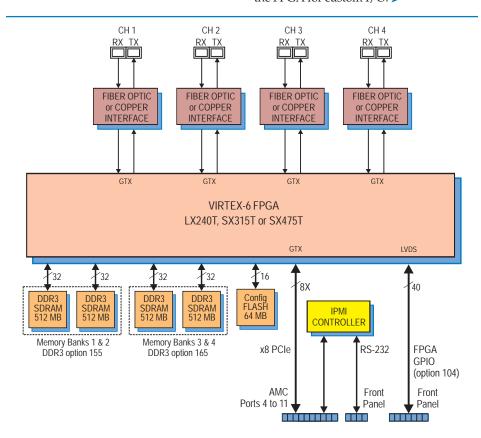

- Supports Xilinx Virtex-6 LXT and SXT FPGAs

- Three 200 MHz 16-bit A/Ds

- One digital upconverter

- Two 800 MHz 16-bit D/As

- Up to 2 GB of DDR3 SDRAM or 32 MB of QDRII+ SRAM

- Sample clock synchronization to an external system reference

- LVPECL clock/sync bus for multimodule synchronization

- PCI Express (Gen. 1 & 2) interface up to x8

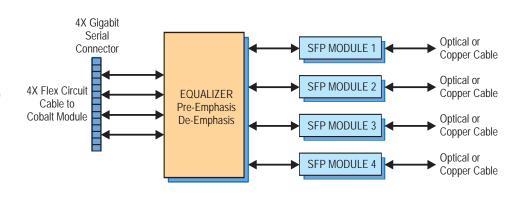

- Optional user-configurable gigabit serial interface

- Optional LVDS connections to the Virtex-6 FPGA for custom I/O

#### **General Information**

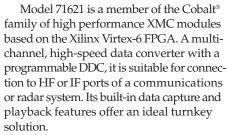

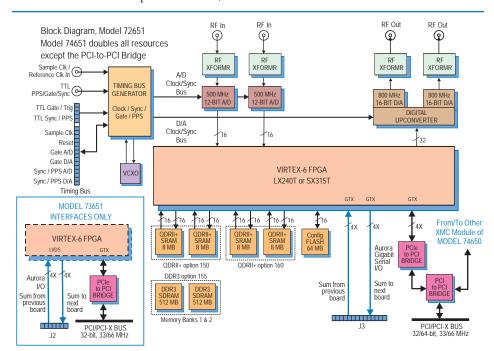

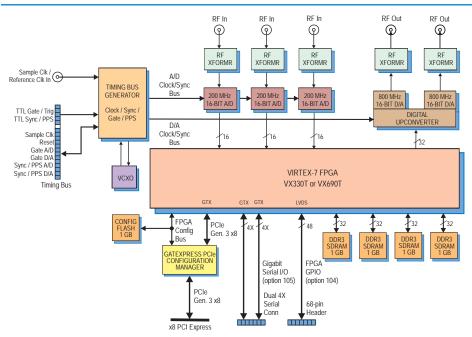

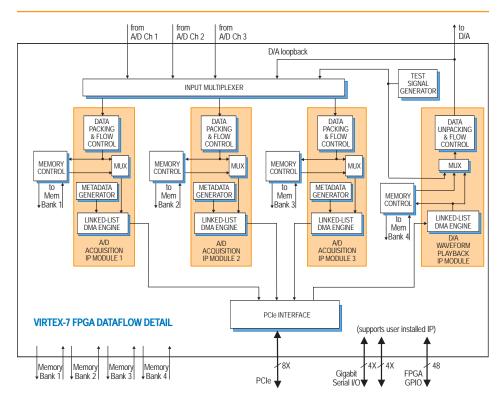

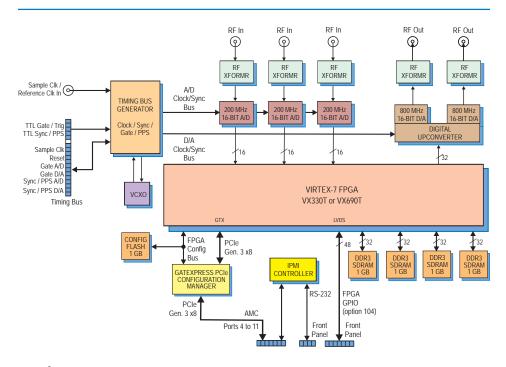

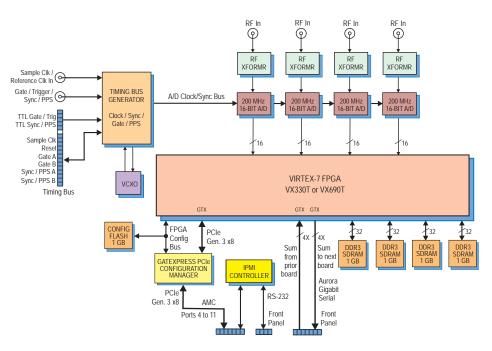

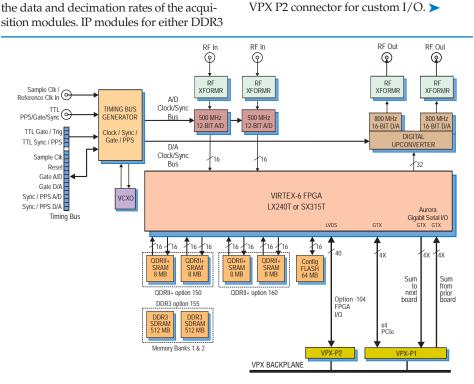

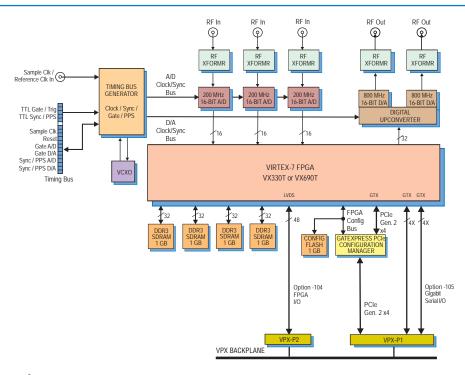

Model 71620 is a member of the Cobalt® family of high performance XMC modules based on the Xilinx Virtex-6 FPGA. A multichannel, high-speed data converter, it is suitable for connection to HF or IF ports of a communications or radar system. Its builtin data capture and playback features offer an ideal turnkey solution.

It includes three A/Ds, two D/As and four banks of memory. In addition to supporting PCI Express Gen. 2 as a native interface, the Model 71620 includes general purpose and gigabit serial connectors for application-specific I/O .

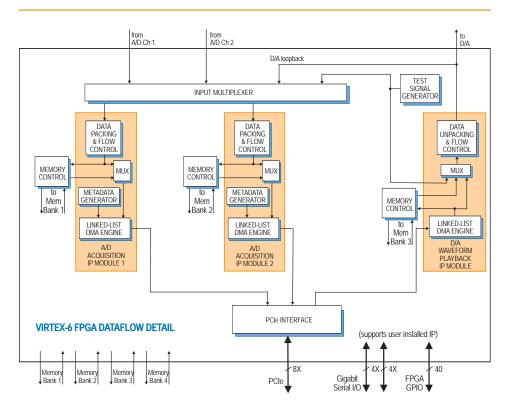

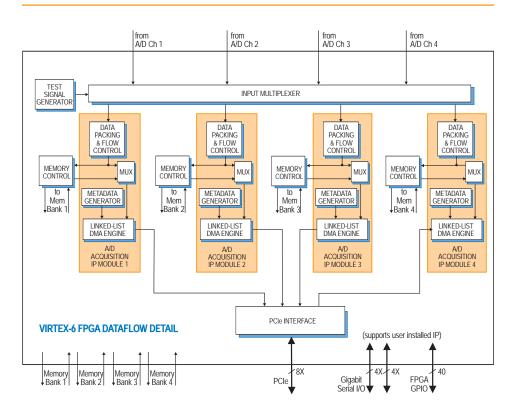

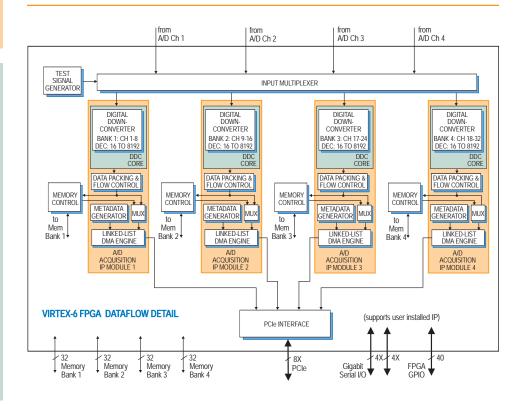

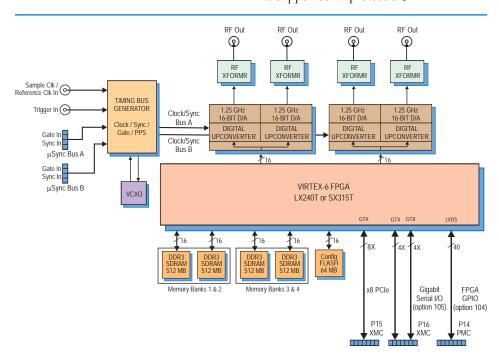

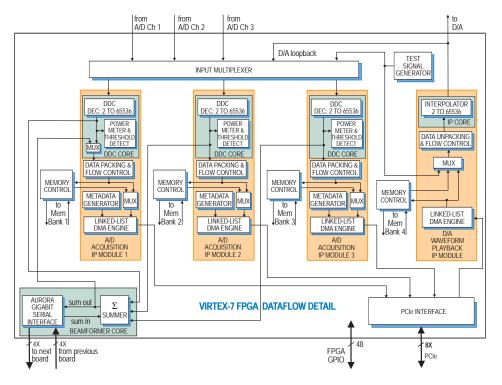

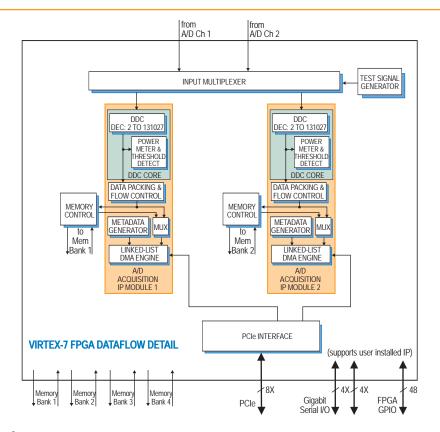

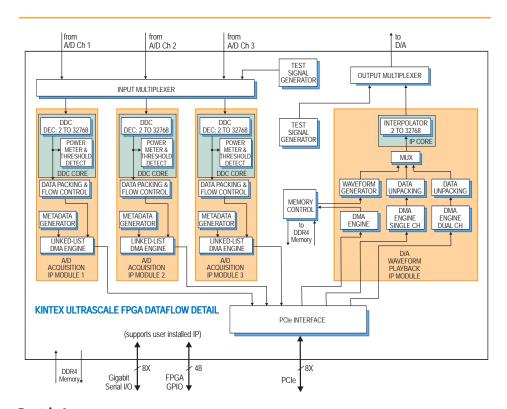

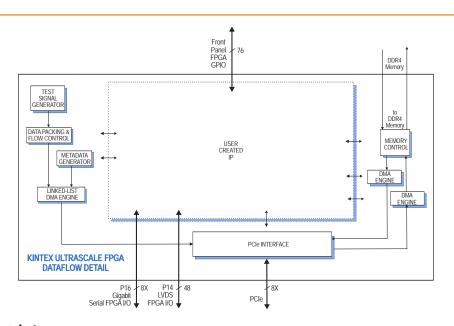

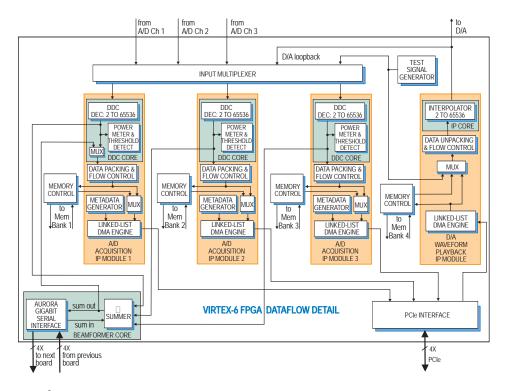

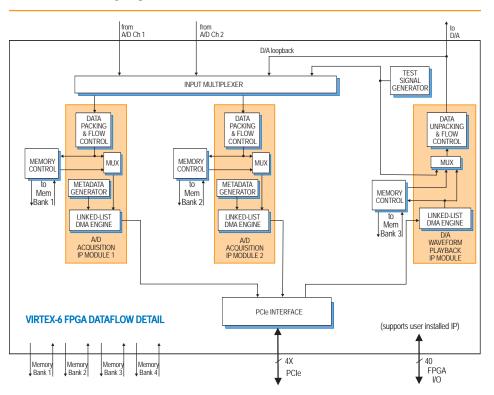

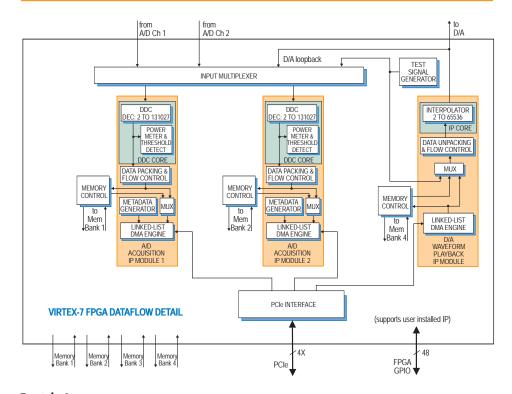

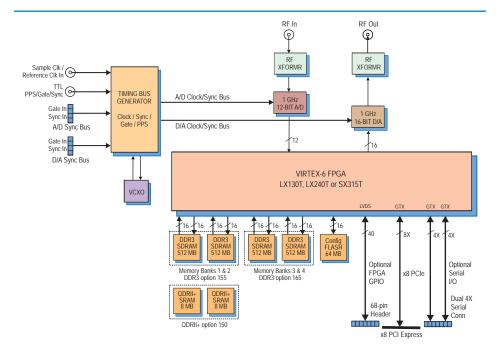

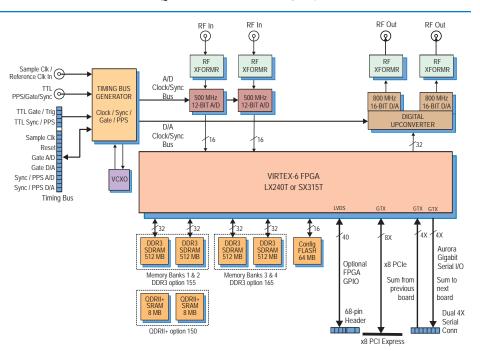

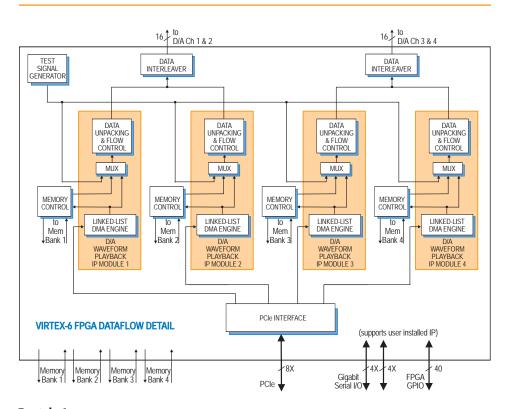

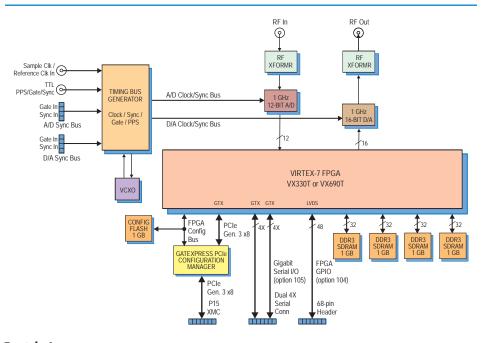

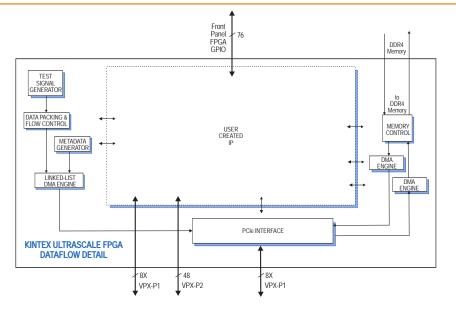

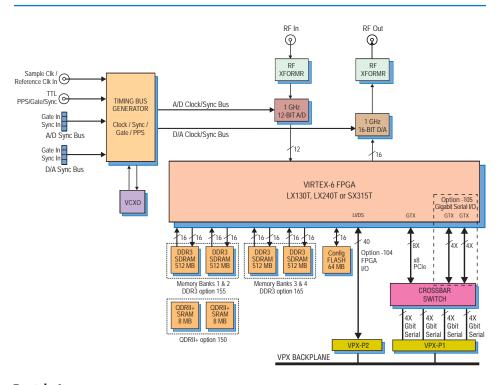

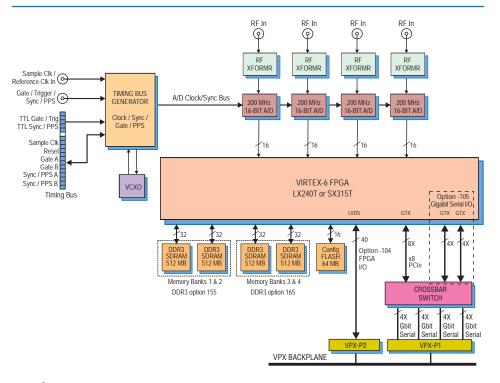

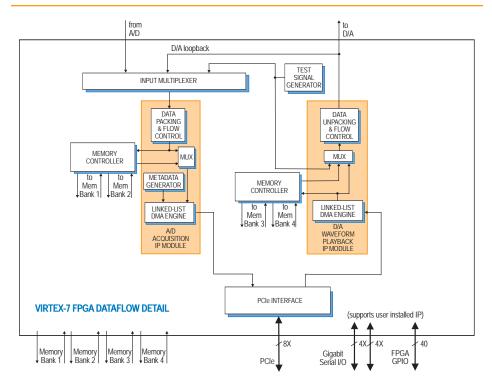

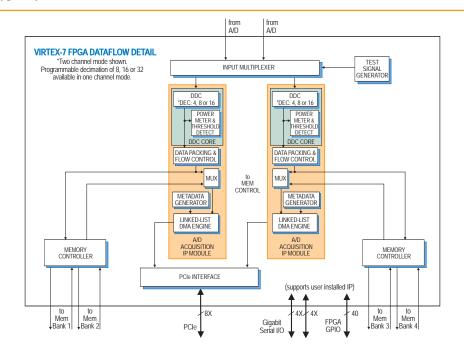

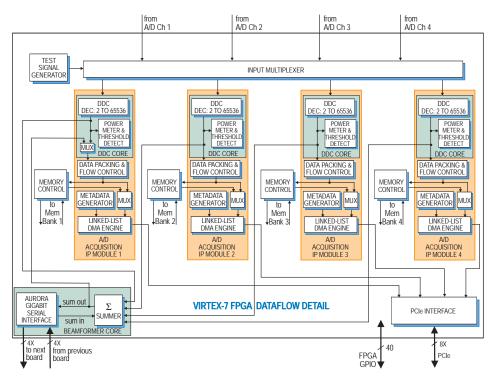

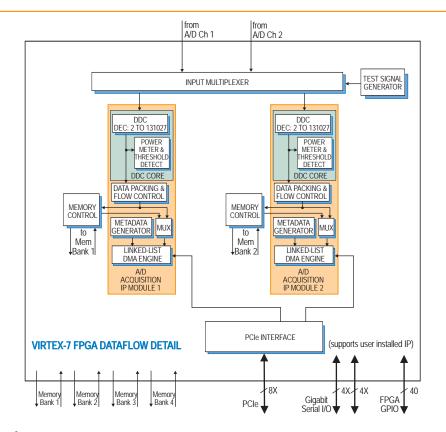

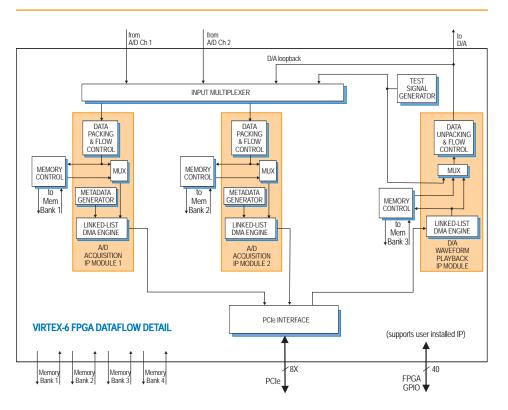

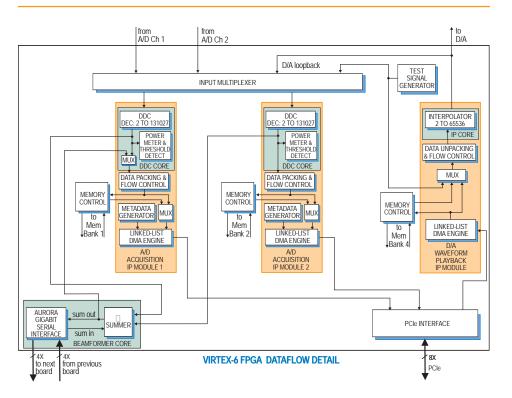

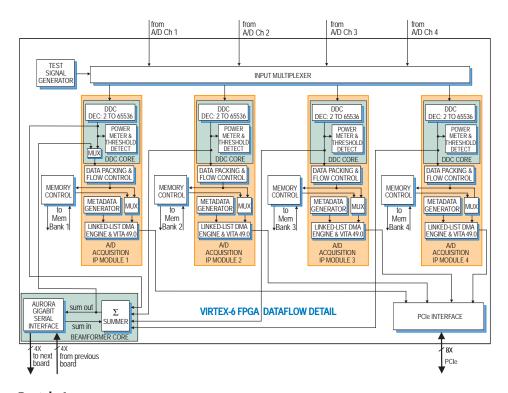

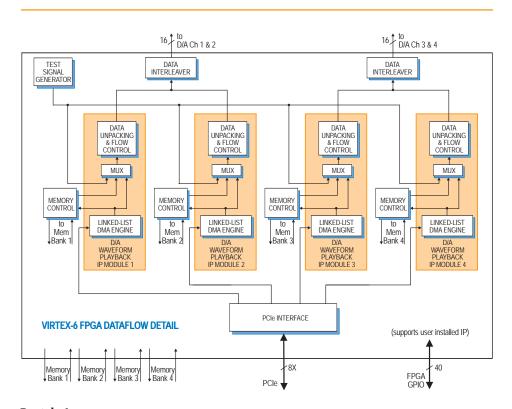

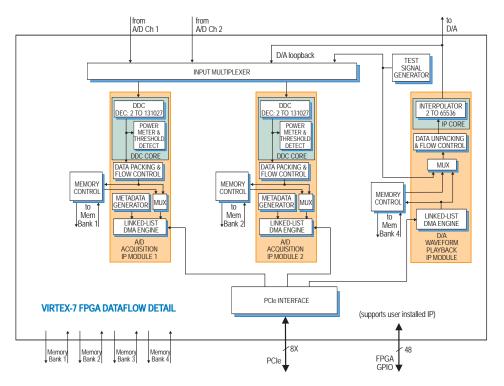

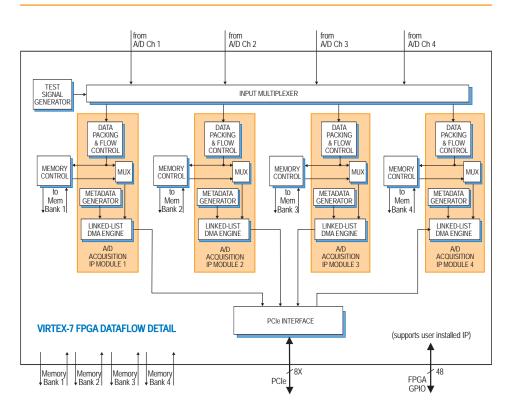

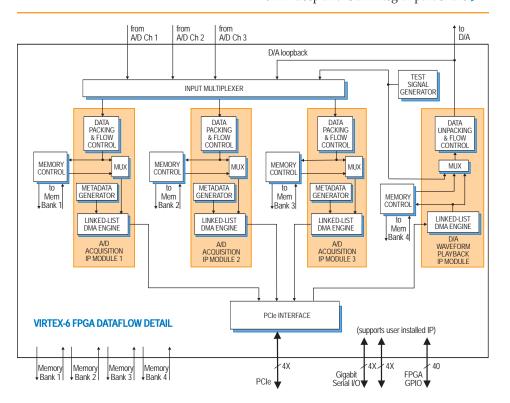

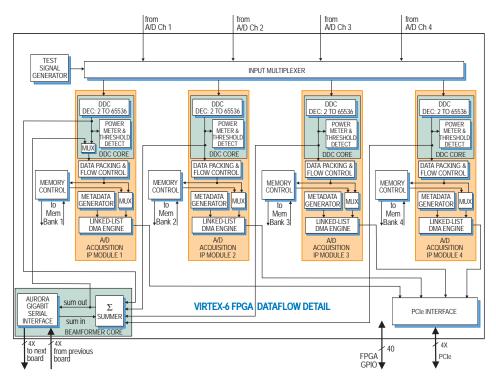

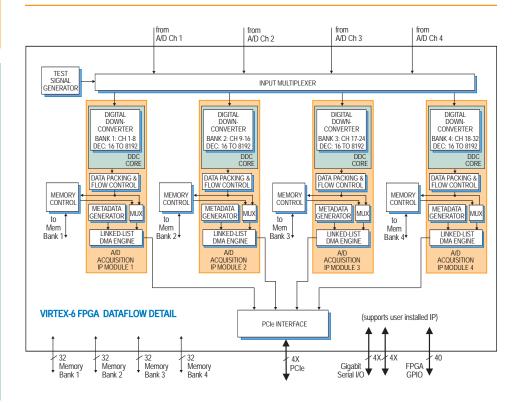

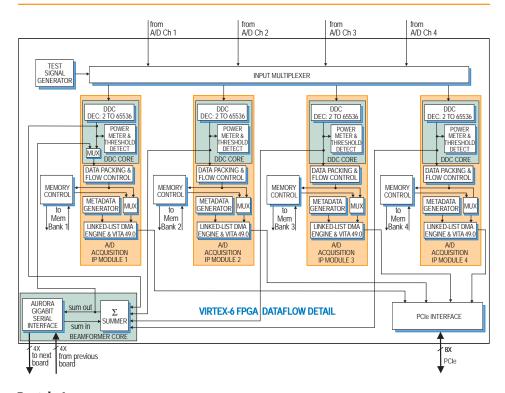

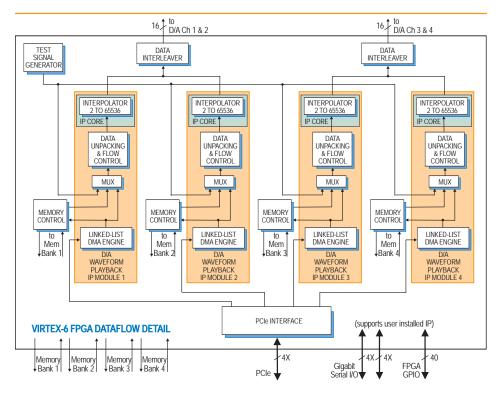

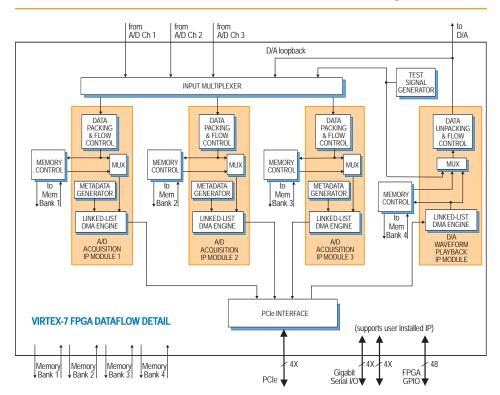

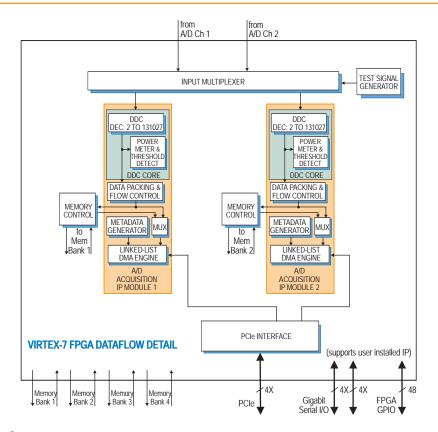

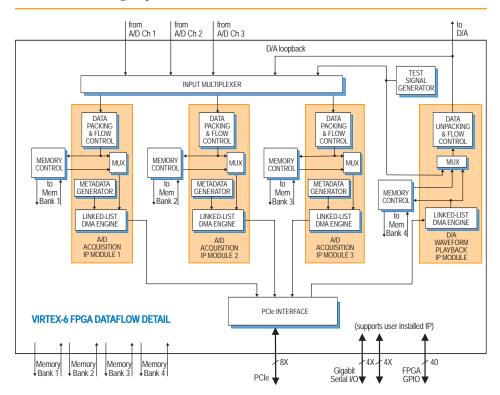

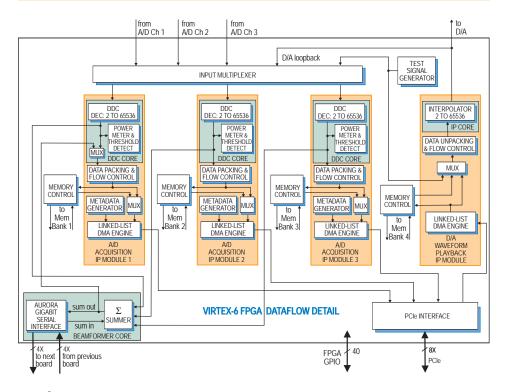

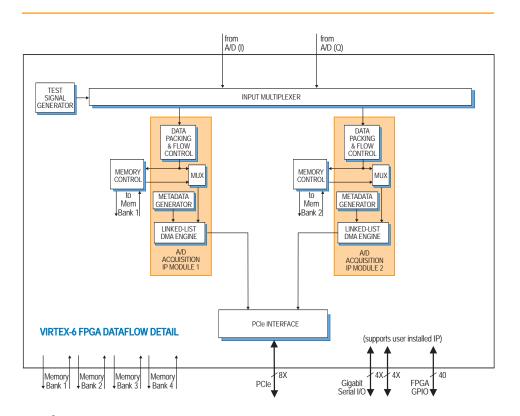

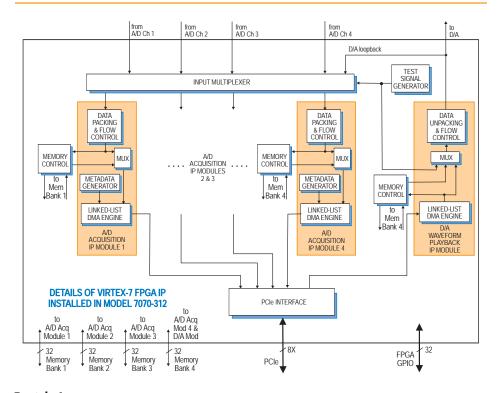

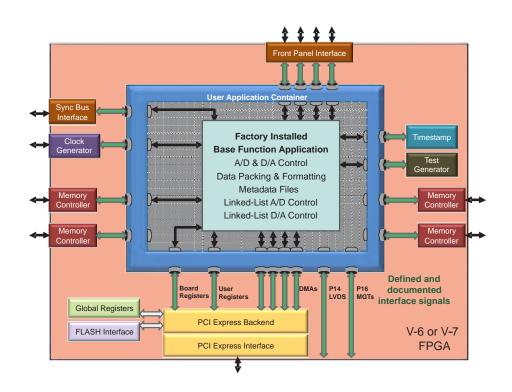

#### **The Cobalt Architecture**

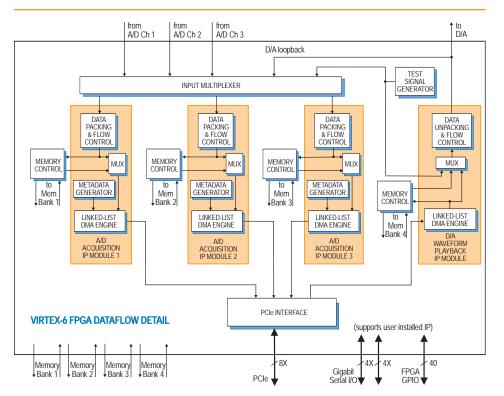

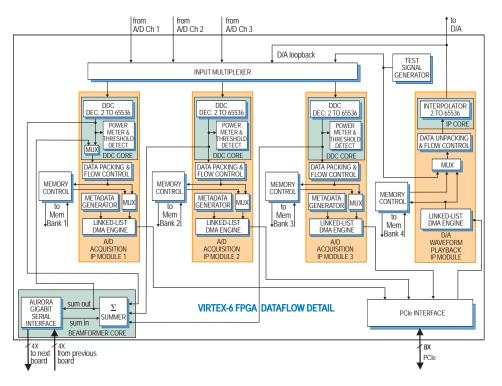

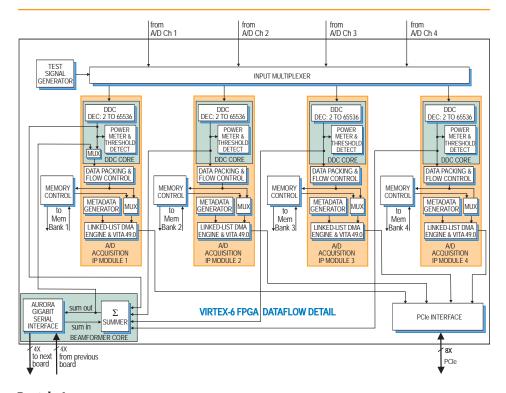

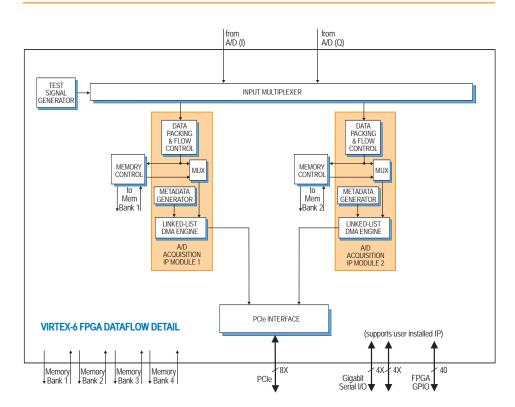

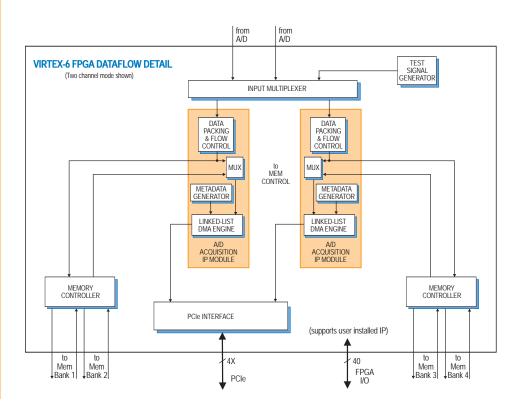

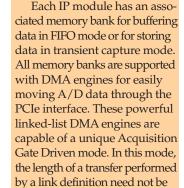

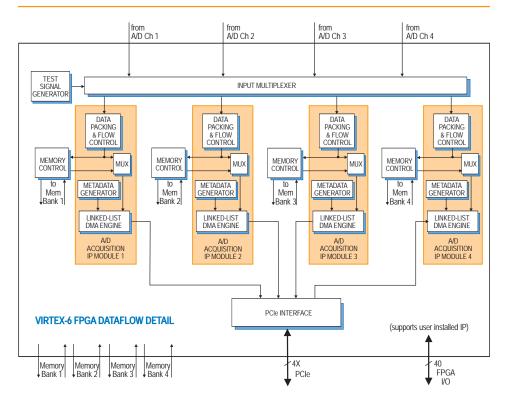

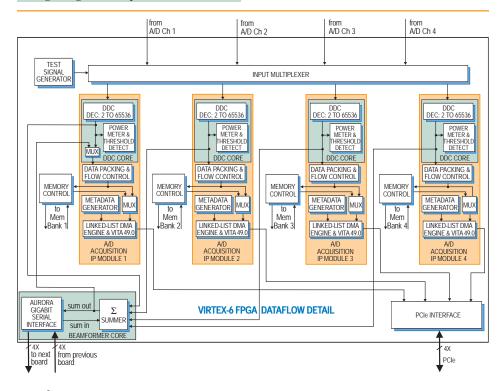

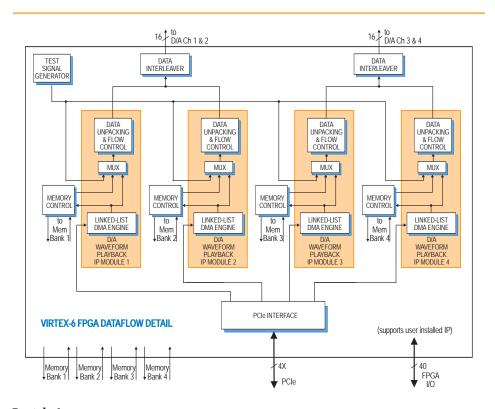

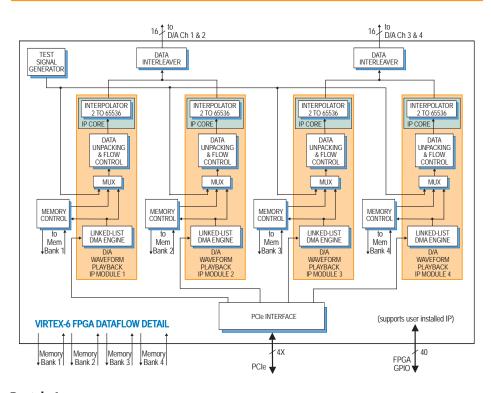

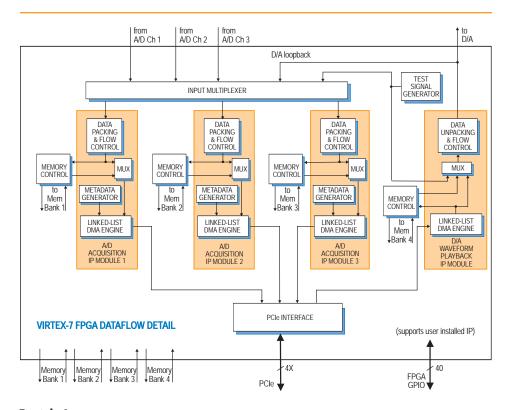

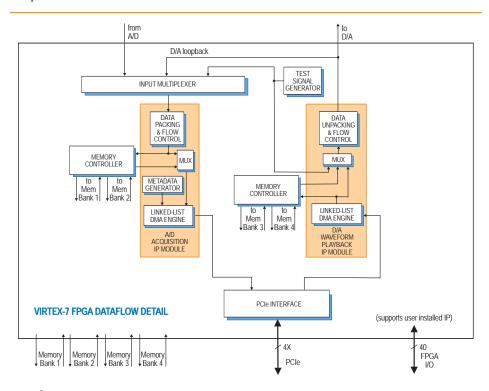

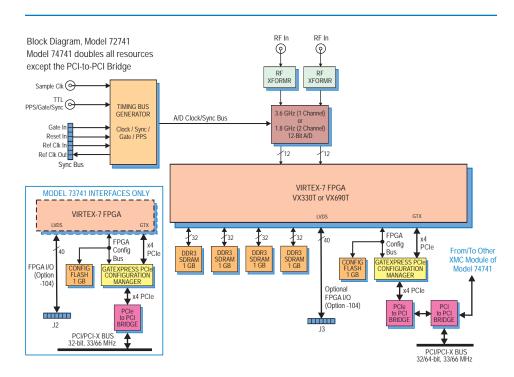

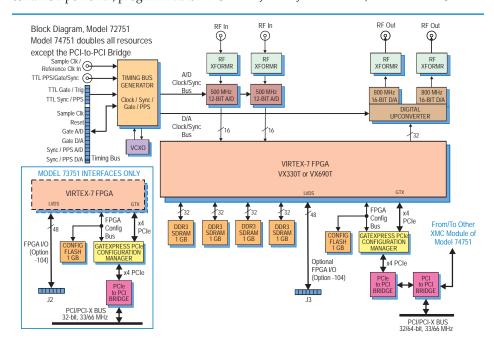

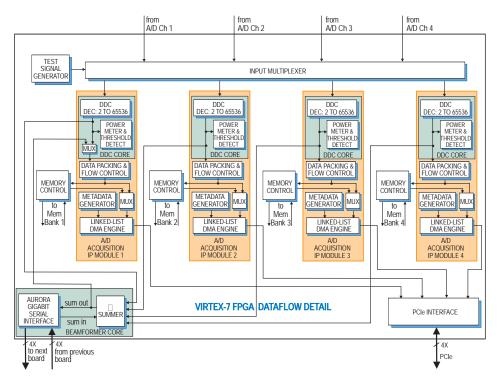

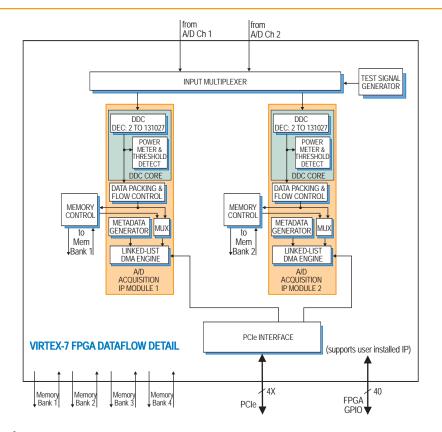

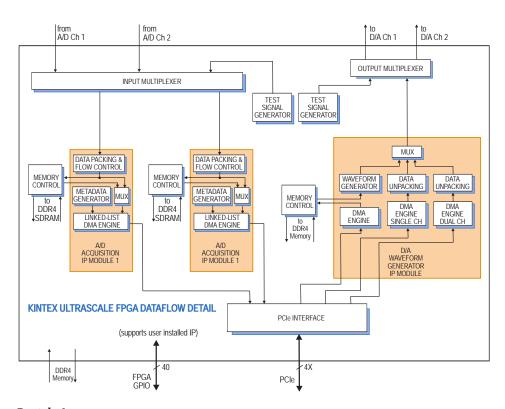

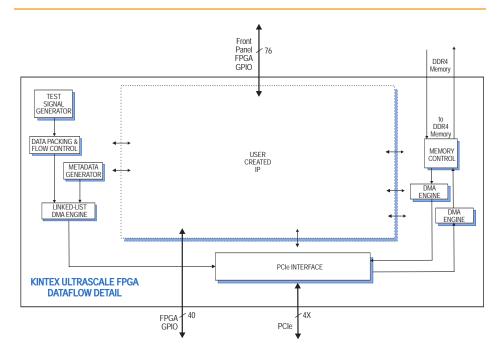

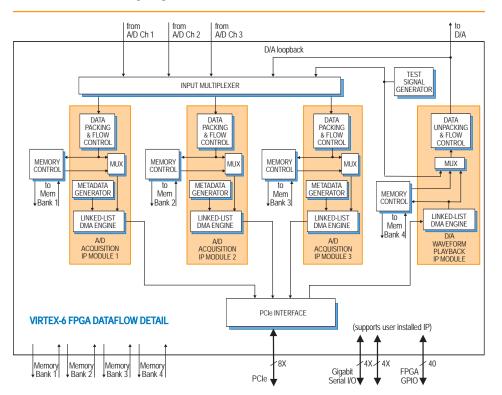

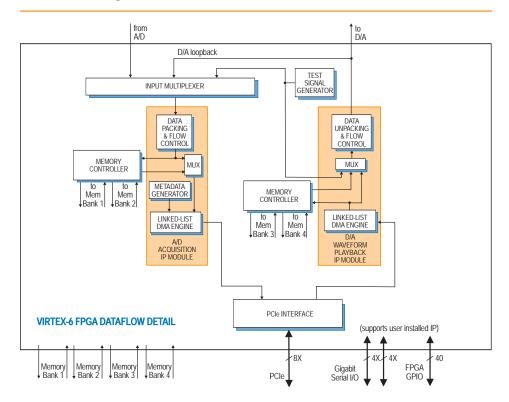

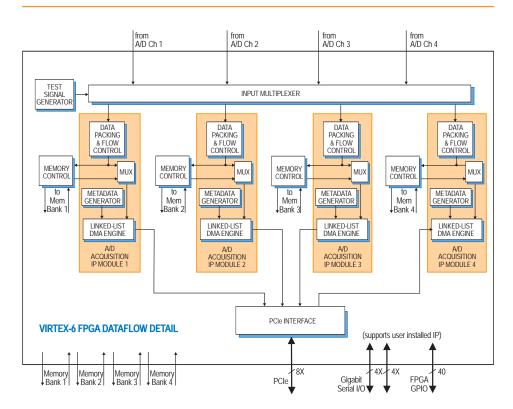

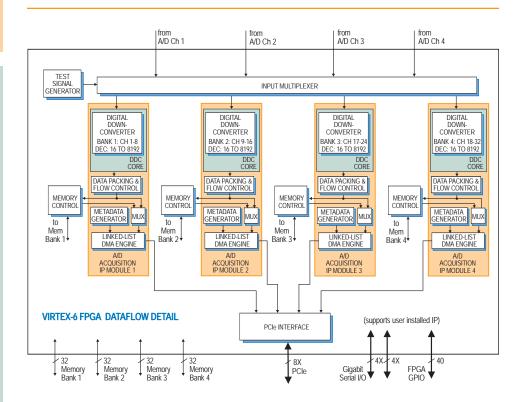

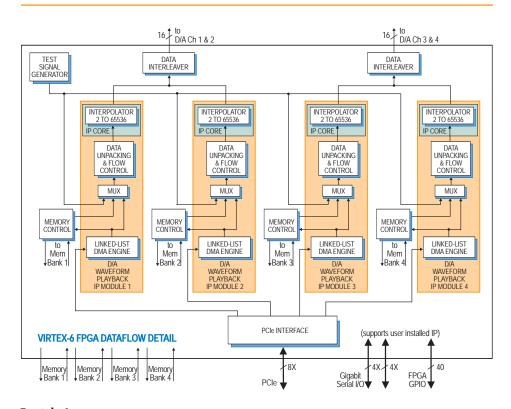

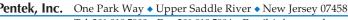

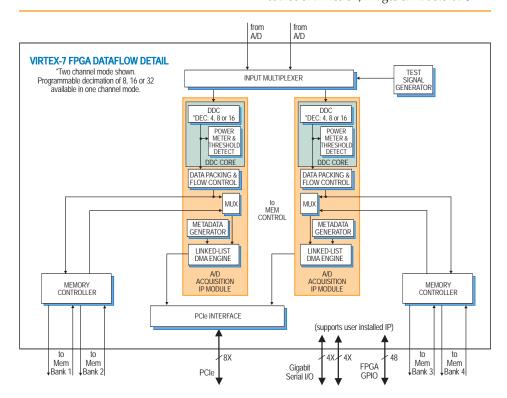

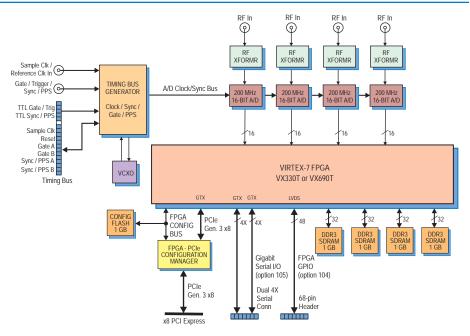

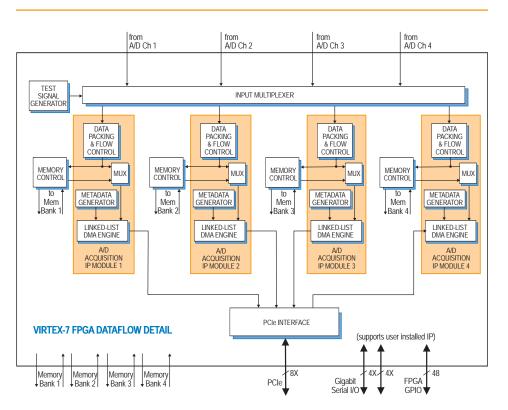

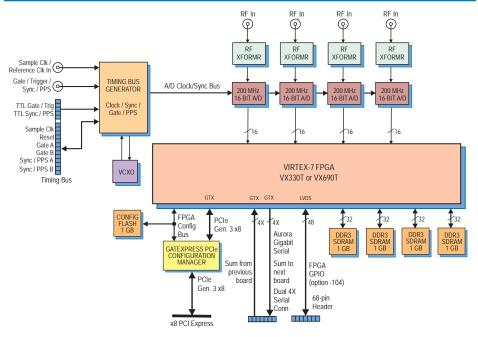

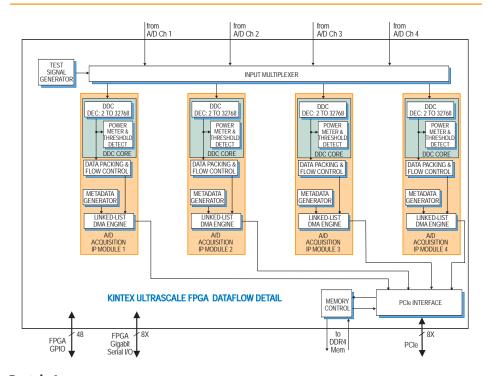

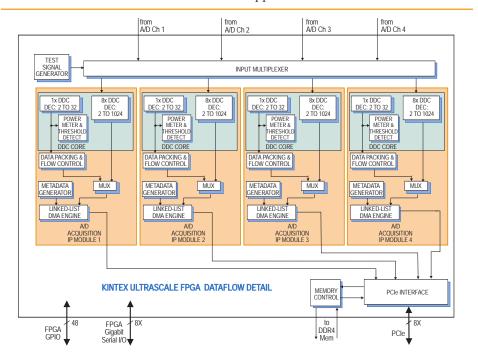

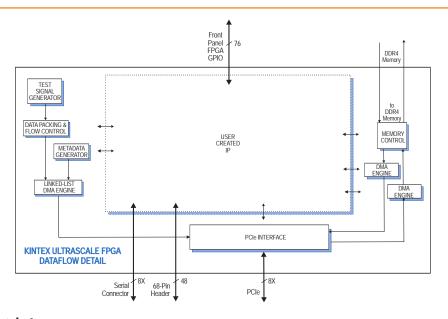

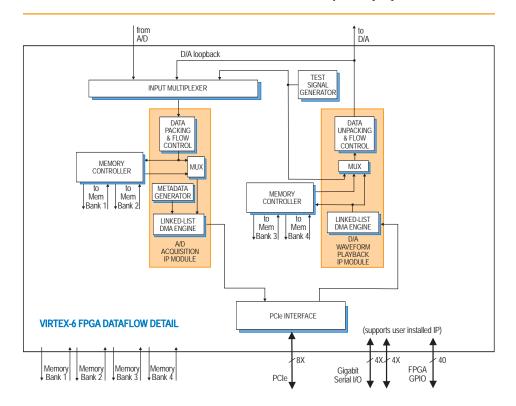

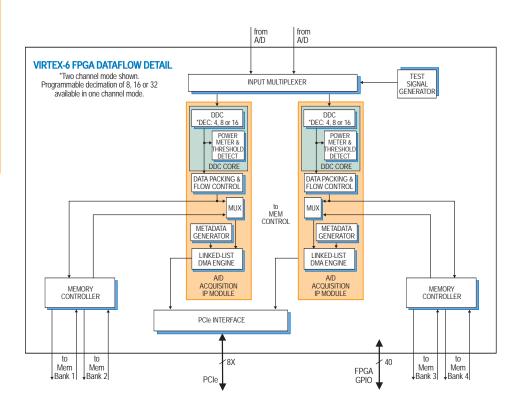

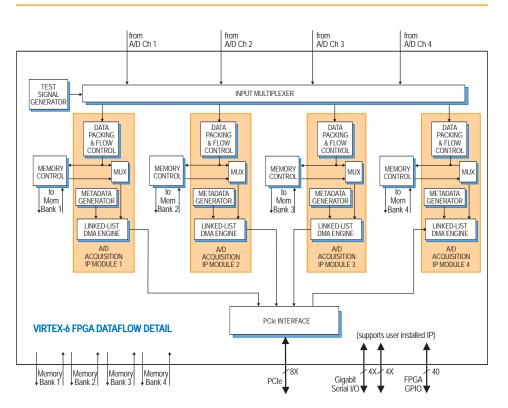

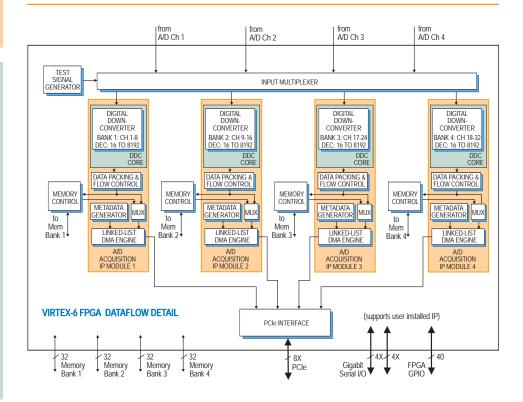

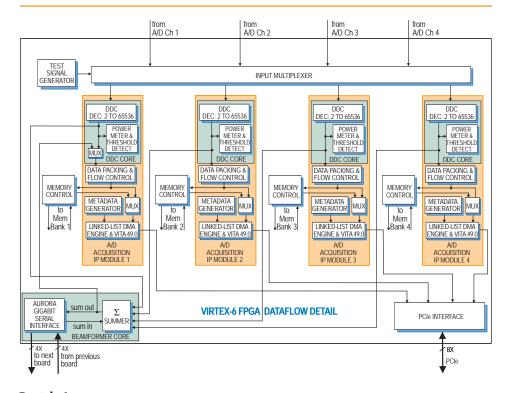

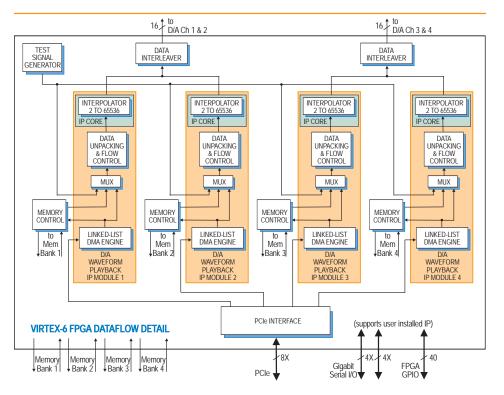

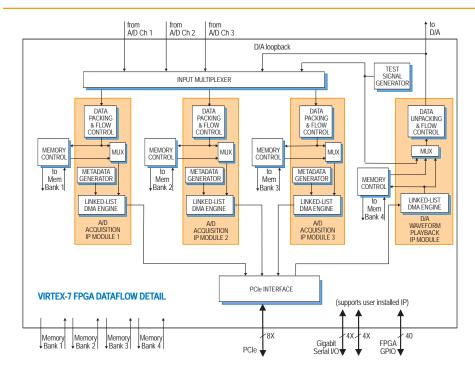

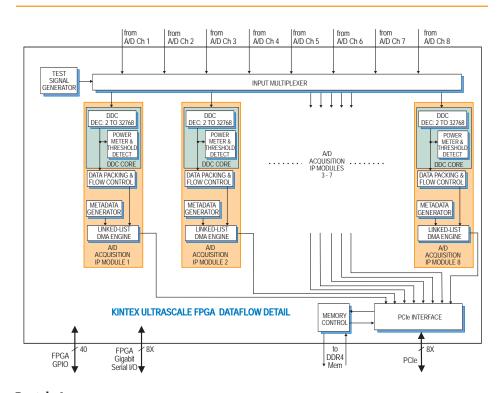

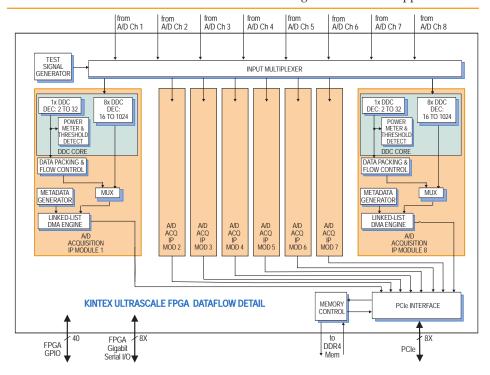

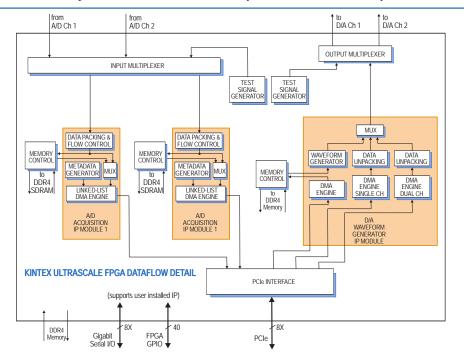

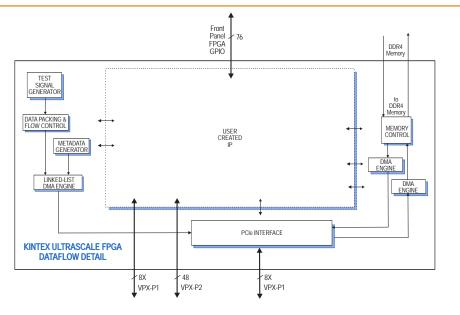

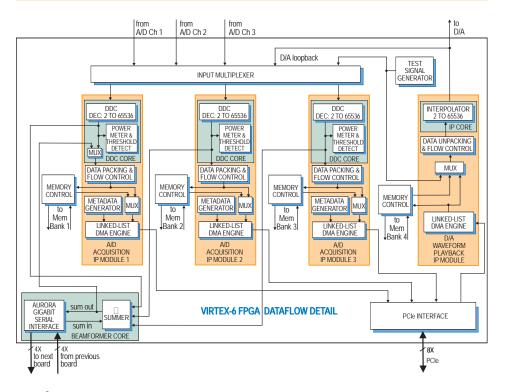

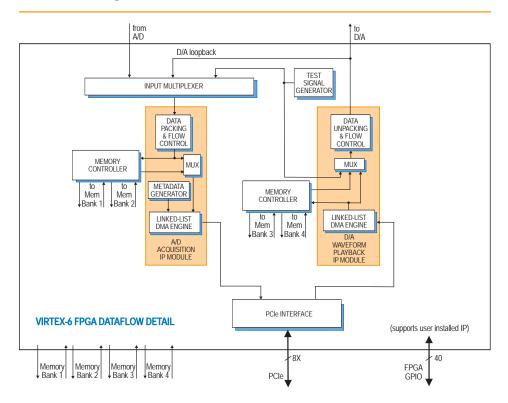

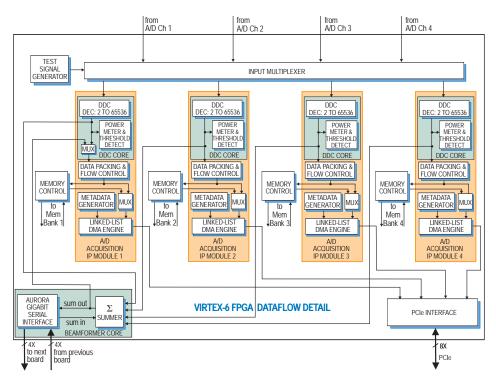

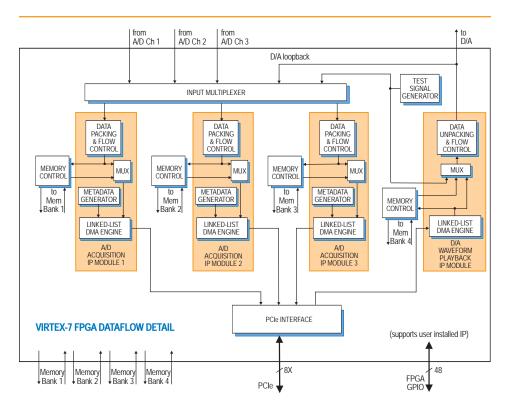

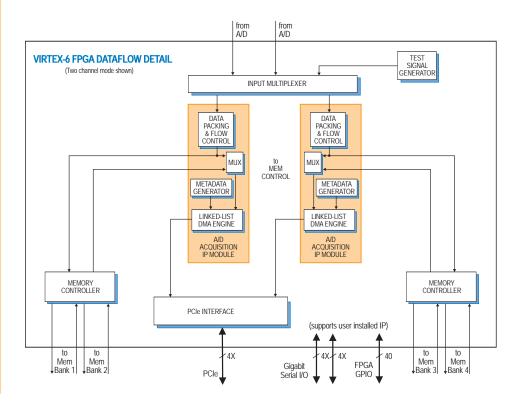

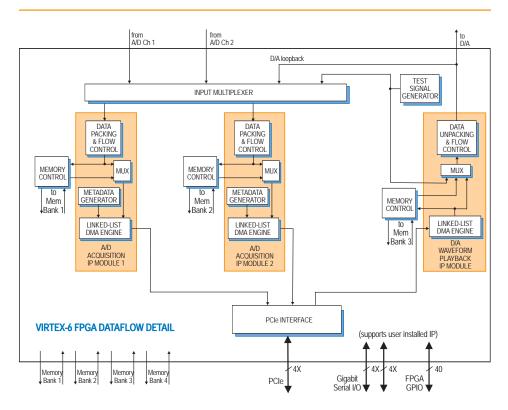

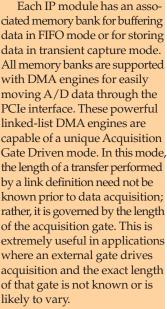

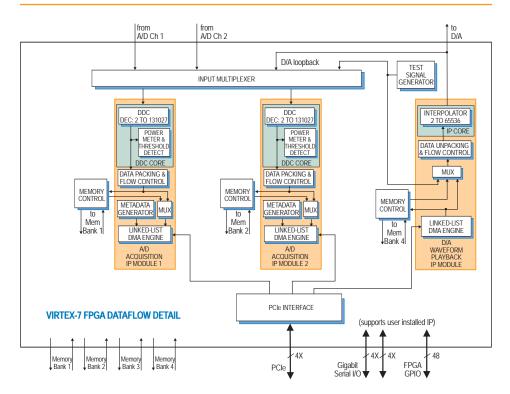

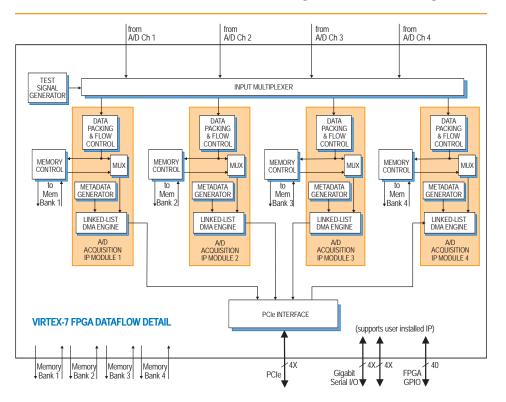

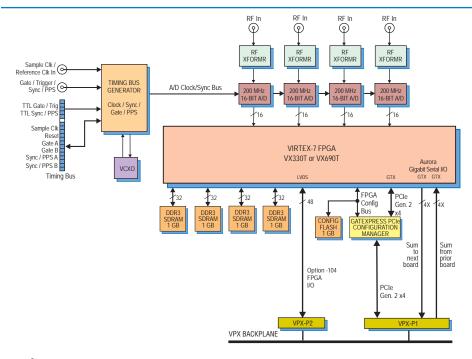

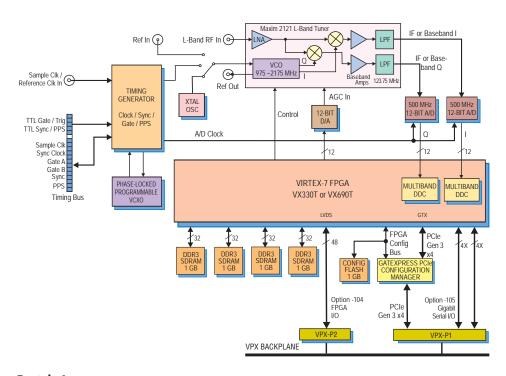

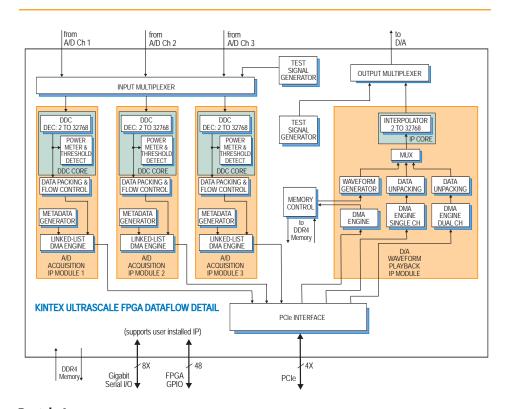

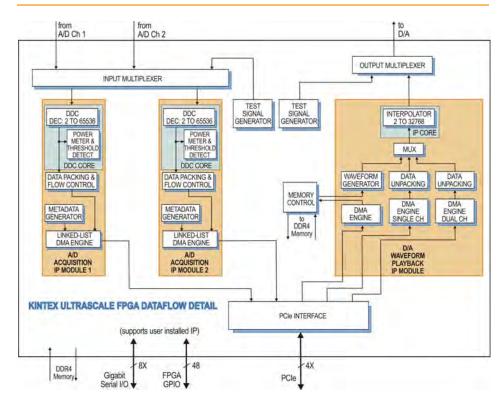

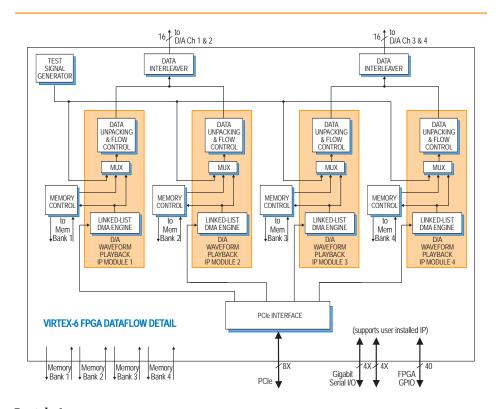

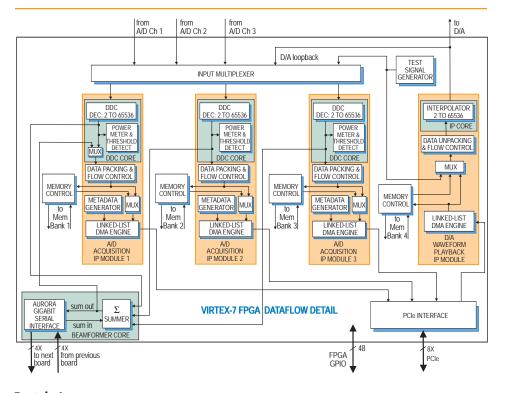

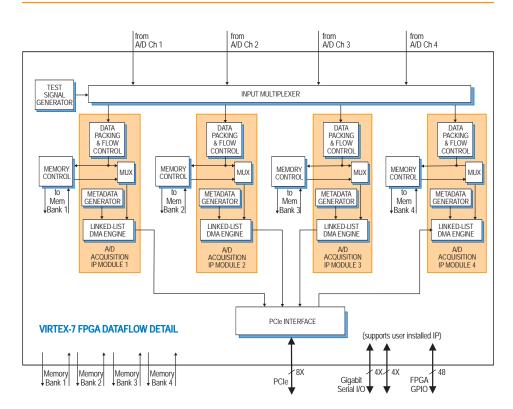

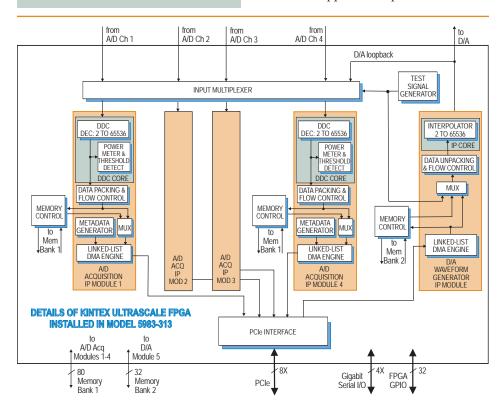

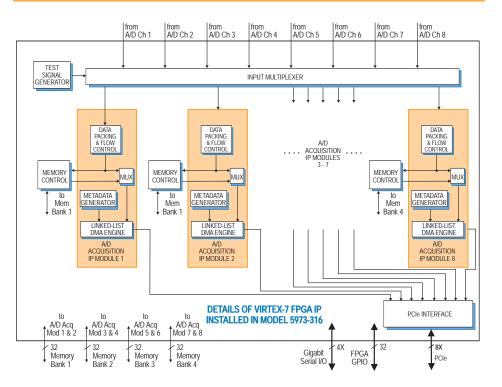

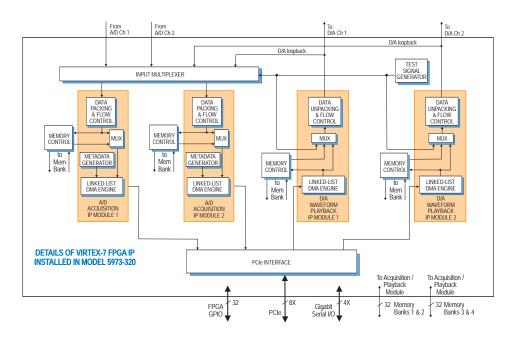

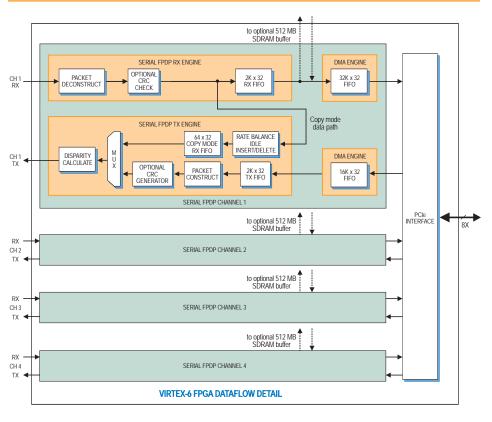

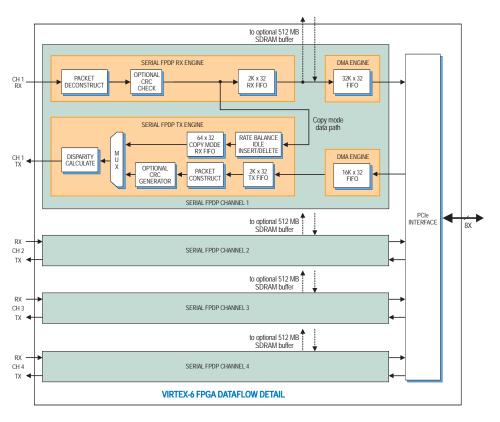

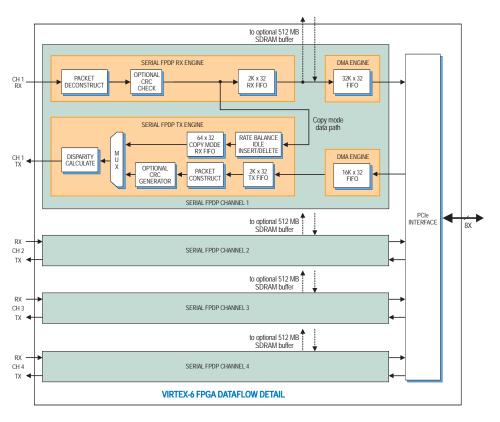

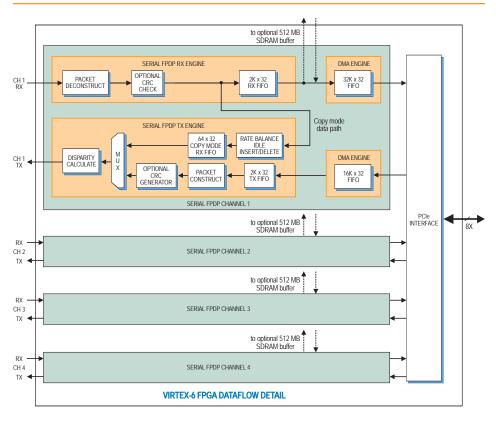

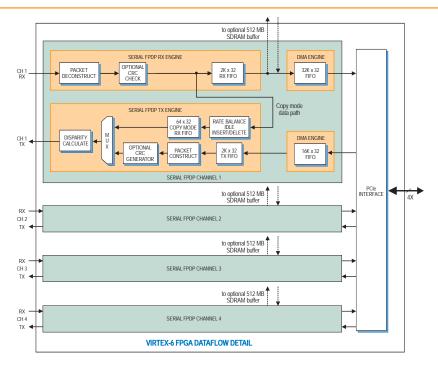

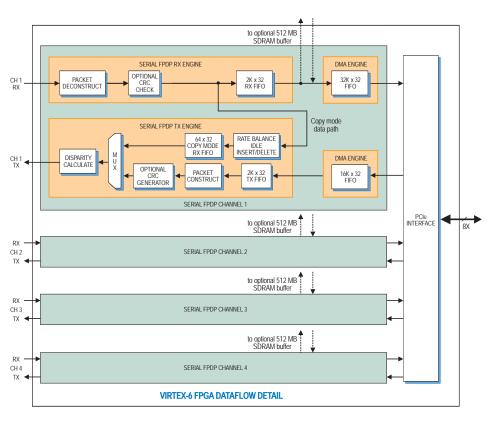

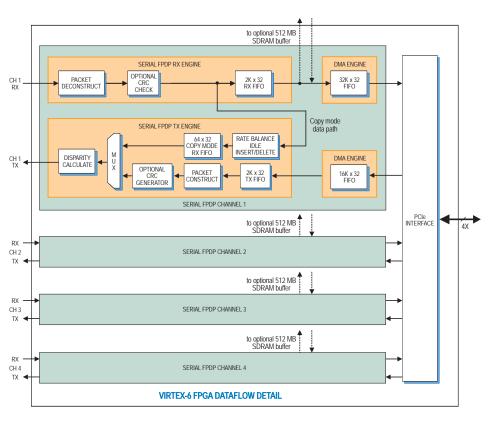

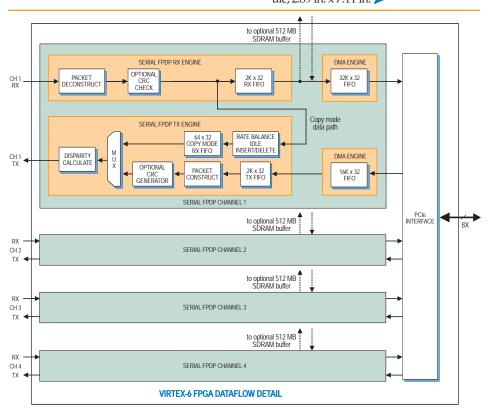

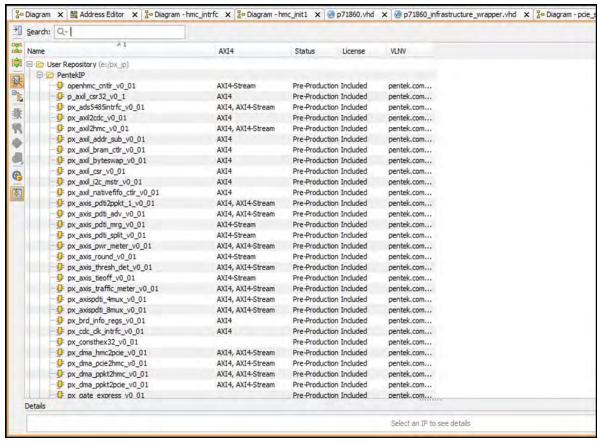

The Pentek Cobalt Architecture features a Virtex-6 FPGA. All of the board's data and control paths are accessible by the FPGA, enabling factory-installed functions including data multiplexing, channel selection, data packing, gating, triggering and memory control. The Cobalt Architecture organizes the FPGA as a container for data processing applications where each function exists as an intellectual property (IP) module.

Each member of the Cobalt family is delivered with factory-installed applications ideally matched to the board's analog interfaces. The 71620 factory-installed functions include three A/D acquisition and a D/A waveform playback IP modules, ideally matched to the board's analog interfaces. IP modules for either DDR3 or QDRII+ memories, a controller for all data clocking and synchro-

nization functions, a test signal generator, and a PCIe interface complete the factory-installed functions and enable the 71620 to operate as a complete turnkey solution, without the need to develop any FPGA IP.

## **Extendable IP Design**

For applications that require specialized functions, users can install their own custom IP for data processing. Pentek GateFlow FPGA Design Kits include all of the factory-installed modules as documented source code. Developers can integrate their own IP with the Pentek factory-installed functions or use the GateFlow kit to completely replace the Pentek IP with their own.

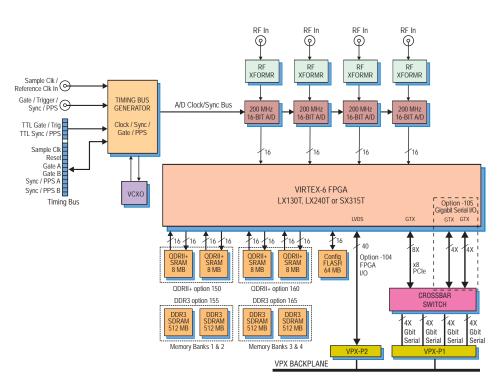

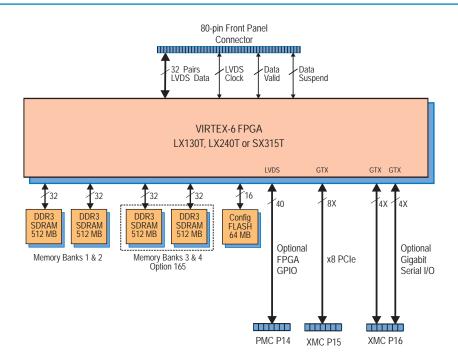

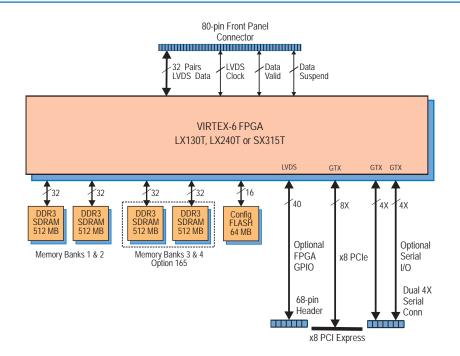

### Xilinx Virtex-6 FPGA

The Virtex-6 FPGA site can be populated with a variety of different FPGAs to match the specific requirements of the processing task. Supported FPGAs include: LX130T, LX240T, or SX315T. The SXT part features 1344 DSP48E slices and is ideal for modulation/demodulation, encoding/decoding, encryption/decryption, and channelization of the signals between transmission and reception. For applications not requiring large DSP resources, one of the lower-cost LXT FPGAs can be installed.

Option -104 installs the P14 PMC connector with 20 pairs of LVDS connections to the FPGA for custom I/O.

Option -105 installs the P16 XMC connector with one 8X or two 4X gigabit links to the FPGA to support serial protocols.

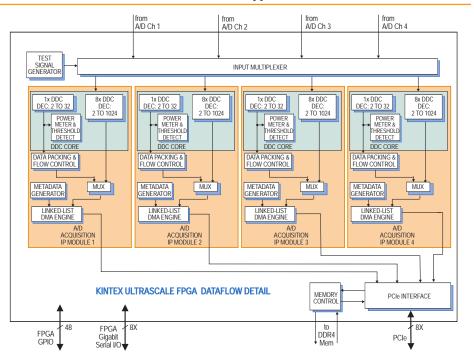

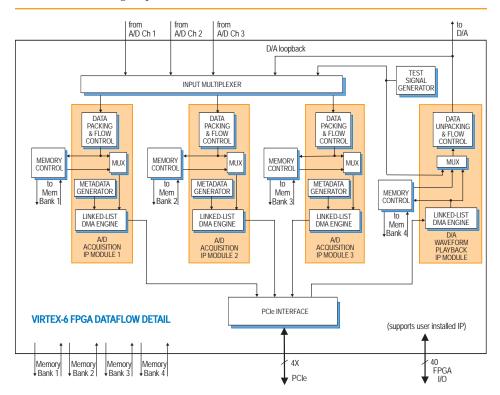

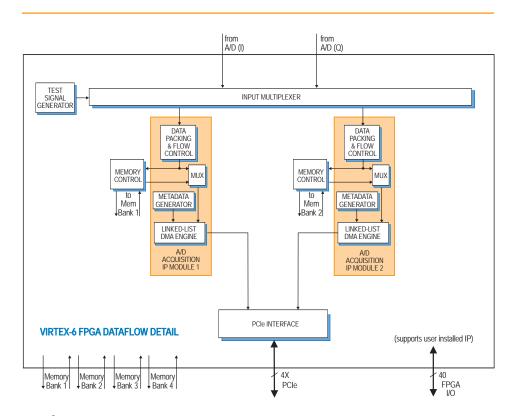

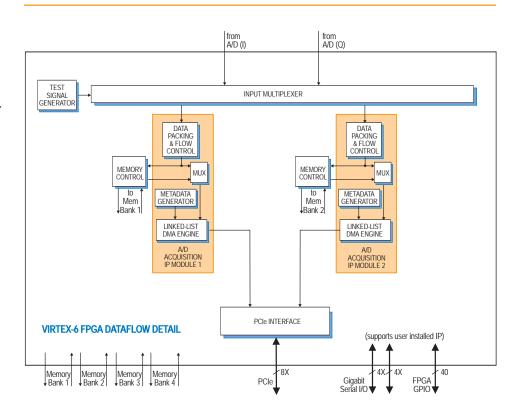

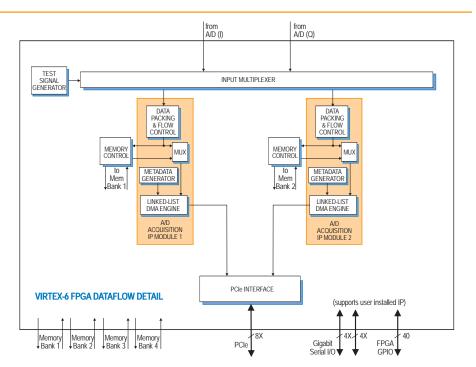

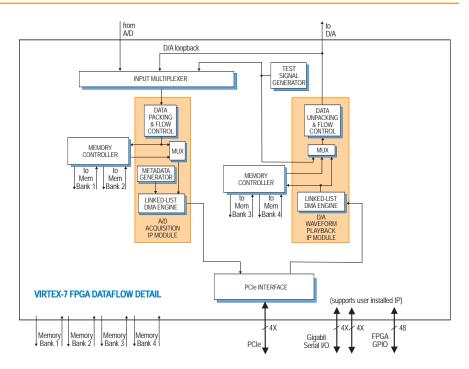

## A/D Acquisition IP Modules

The 71620 features three A/D Acquisition IP Modules for easily capturing and moving data. Each module can receive data from any of the three A/Ds, a test signal generator or from the D/A Waveform Playback IP Module in loopback mode.

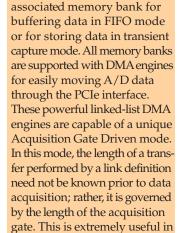

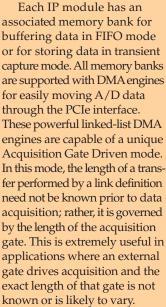

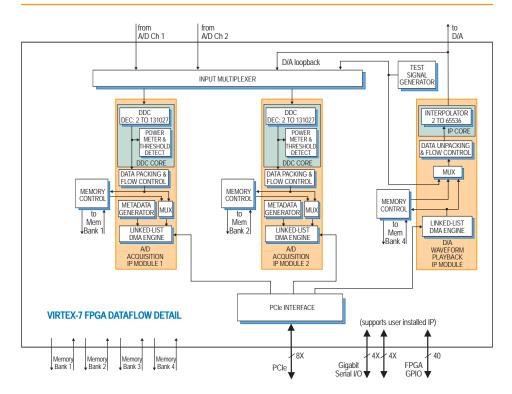

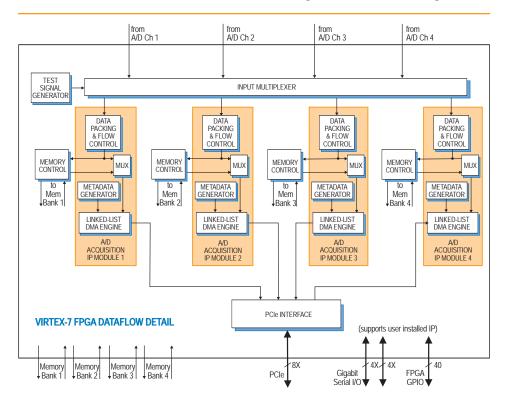

Each IP module has an associated memory bank for buffering data in FIFO mode or for storing data in transient capture mode. All memory banks are supported with DMA engines for easily moving A/D data through the PCIe interface.

These powerful linked-list DMA engines are capable of a unique Acquisition Gate Driven mode. In this mode, the length of a transfer performed by a link definition need not be known prior to data acquisition; rather, it is governed by the length of the acquisition gate. This is extremely useful in applications where an external gate drives acquisition and the exact length of that gate is not known or is likely to vary.

For each transfer, the DMA engine can automatically construct metadata packets containing A/D channel ID, a sample-accurate time stamp and data length information. These actions simplify the host processor's job of identifying and executing on the data.

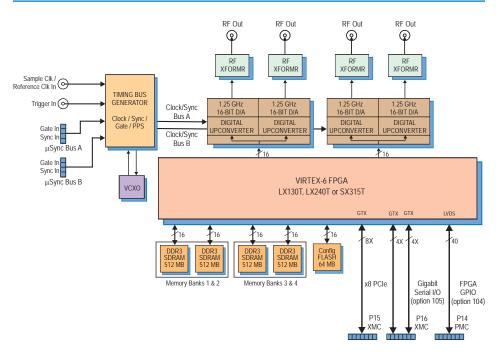

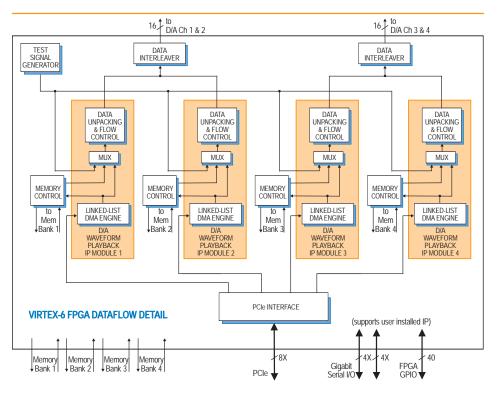

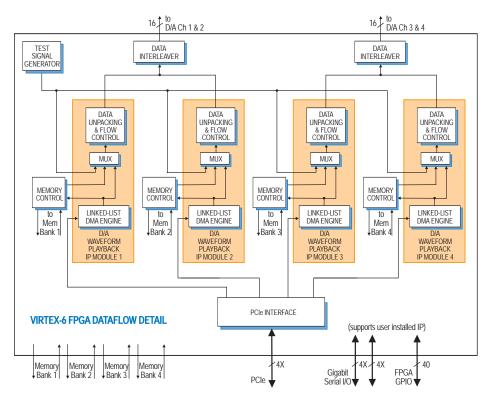

# D/A Waveform Playback IP Module

The Model 71620 factory-installed functions include a sophisticated D/A Waveform Playback IP module. A linked-list controller allows users to easily play back to the dual D/As waveforms stored in either on-board memory or off-board host memory.

Parameters including length of waveform, delay from playback trigger, waveform repetition, etc. can be programmed for each waveform.

Up to 64 individual link entries can be chained together to create complex waveforms with a minimum of programming.

### ➤ A/D Converter Stage

The front end accepts three full-scale analog HF or IF inputs on front panel SSMC connectors at +8 dBm into 50 ohms with transformer coupling into three Texas Instruments ADS5485 200 MHz, 16-bit A/D converters.

The digital outputs are delivered into the Virtex-6 FPGA for signal processing, data capture or for routing to other module resources.

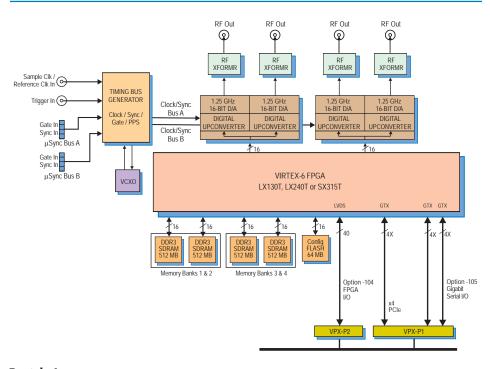

## Digital Upconverter and D/A Stage

A TI DAC5688 DUC (digital upconverter) and D/A accepts a baseband real or complex data stream from the FPGA and provides that input to the upconvert, interpolate and dual D/A stages.

When operating as a DUC, it interpolates and translates real or complex baseband input signals to any IF center frequency up to 360 MHz. It delivers real or quadrature (I+Q) analog outputs to the dual 16-bit D/A converter. Analog output is through a pair of front panel SSMC connectors.

If translation is disabled, the DAC5688 acts as a dual interpolating 16-bit D/A with output sampling rates up to 800 MHz. In both modes the DAC5688 provides interpolation factors of 2x, 4x and 8x.

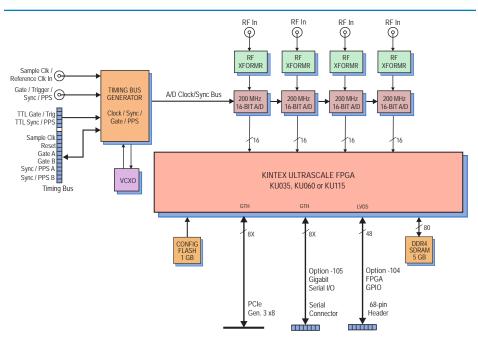

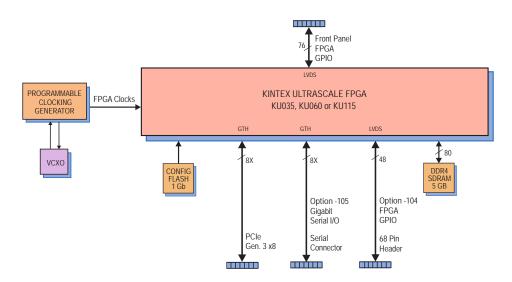

## **Clocking and Synchronization**

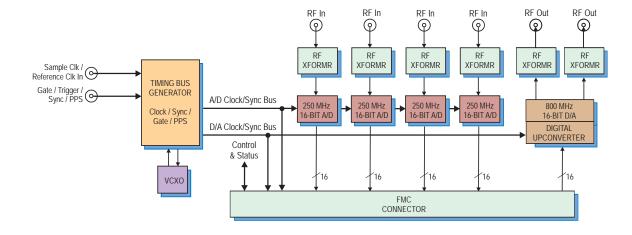

Two internal timing buses provide either a single clock or two different clock rates to the A/D and D/A signal paths.

Each timing bus includes a clock, sync and a gate or trigger signal. An on-board clock generator receives an external sample clock from the front panel SSMC connector. This clock can be used directly for either the A/D or D/A sections or can be divided by a built-in clock synthesizer circuit to provide different A/D and D/A clocks. In an alternate mode, the sample clock can be sourced from an on-board programmable VCXO (Voltage-Controlled Crystal Oscillator). In this mode, the front panel SSMC connector can be used to provide a 10 MHz reference clock for synchronizing the internal oscillator.

A front panel 26-pin LVPECL Clock/Sync connector allows multiple modules to be synchronized. In the slave mode, it accepts LVPECL inputs that drive the clock, sync and gate signals. In the master mode, the LVPECL bus can drive the timing signals for synchronizing multiple modules.

Multiple 71620's can be driven from the LVPECL bus master, supporting synchronous sampling and sync functions across all connected modules.

## **Memory Resources**

The 71620 architecture supports up to four independent memory banks which can be configured with all QDRII+ SRAM, DDR3 SDRAM, or as combination of two banks of each type of memory.

Each QDRII+ SRAM bank can be up to 8 MB deep and is an integral part of the

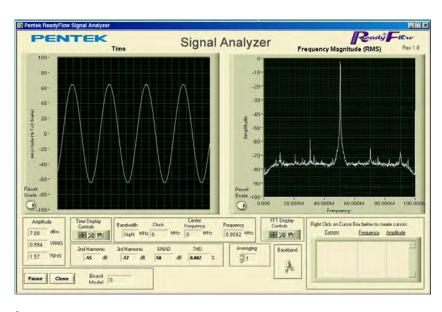

## **Model 8266**

The Model 8266 is a fullyintegrated PC development system for Pentek Cobalt, Onyx and Flexor PCI Express boards. It was created to save engineers and system integrators the time and expense associated with building and testing a development system that ensures optimum performance of Pentek boards.

## **Ordering Information**

| Model | Description                                                            |

|-------|------------------------------------------------------------------------|

| 71620 | 3-Channel 200 MHz A/D and 2-Channel 800 MHz D/A with Virtex-6 FPGA XMC |

| Options: |                                                          |

|----------|----------------------------------------------------------|

| -062     | XC6VLX240T FPGA                                          |

| -064     | XC6VSX315T FPGA                                          |

| -104     | LVDS FPGA I/O through P14 connector                      |

| -105     | Gigabit serial FPGA I/O through P16 connector            |

| -150     | Two 8 MB QDRII+ SRAM<br>Memory Banks<br>(Banks 1 and 2)  |

| -160     | Two 8 MB QDRII+ SRAM<br>Memory Banks<br>(Banks 3 and 4)  |

| -155     | Two 512 MB DDR3<br>SDRAM Memory Banks<br>(Banks 1 and 2) |

| -165     | Two 512 MB DDR3<br>SDRAM Memory Banks<br>(Banks 3 and 4) |

Contact Pentek for availability of rugged and conduction-cooled versions

| Model | Description |

|-------|-------------|

| 8266  | PC Developm |

PC Development System See 8266 Datasheet for Options

> module's DMA capabilities, providing FIFO memory space for creating DMA packets. For applications requiring deep memory resources, DDR3 SDRAM banks can each be up to 512 MB deep. Built-in memory functions include an A/D data transient capture mode and D/A waveform playback mode.

In addition to the factory-installed functions, custom user-installed IP within the FPGA can take advantage of the memories for many other purposes.

## **XMC Interface**

The Model 71620 complies with the VITA 42.0 XMC specification. Two connectors each provide dual 4X links or a single 8X link with up to a 6 GHz bit clock. With dual XMC connectors, the 71620 supports x8 PCIe on the first XMC connector leaving the second connector free to support userinstalled transfer protocols specific to the target application.

#### **PCI Express Interface**

The Model 71620 includes an industrystandard interface fully compliant with PCI Express Gen. 1 & 2 bus specifications. Supporting PCIe links up to x8, the interface includes multiple DMA controllers for efficient transfers to and from the module.

## **Specifications**

#### Front Panel Analog Signal Inputs

**Input Type:** Transformer-coupled, front panel female SSMC connectors Transformer Type: Coil Craft WBC4-6TLB

Full Scale Input: +8 dBm into 50 ohms 3 dB Passband: 300 kHz to 700 MHz

#### A/D Converters

**Type:** Texas Instruments ADS5485 Sampling Rate: 10 MHz to 200 MHz Resolution: 16 bits

#### D/A Converters

Type: Texas Instruments DAC5688 **Input Data Rate:** 250 MHz max. Output IF: DC to 400 MHz max. Output Signal: 2-channel real or 1-channel with frequency translation Output Sampling Rate: 800 MHz max.

with interpolation

Resolution: 16 bits

#### Front Panel Analog Signal Outputs

Output Type: Transformer-coupled, front panel female SSMC connectors Transformer Type: Coil Craft WBC4-6TLB

Full Scale Output: +4 dBm into 50 ohms 3 dB Passband: 300 kHz to 700 MHz

Sample Clock Sources: On-board clock synthesizer generates two clocks: one A/D clock and one D/A clock

#### **Clock Synthesizer**

Clock Source: Selectable from on-board programmable VCXO (10 to 810 MHz), front panel external clock or LVPECL timing bus

**Synchronization:** VCXO can be locked to an external 4 to 180 MHz PLL system reference, typically 10 MHz

Clock Dividers: External clock or VCXO can be divided by 1, 2, 4, 8, or 16 for the A/D clock

#### **External Clock**

Type: Front panel female SSMC connector, sine wave, 0 to +10 dBm, AC-coupled, 50 ohms, accepts 10 to 800 MHz sample clock or PLL system reference

Timing Bus: 26-pin connector LVPECL bus includes, clock/sync/gate/PPS inputs and outputs; TTL signal for gate/ trigger and sync/PPS inputs

#### Field Programmable Gate Array

Standard: Xilinx Virtex-6 XC6VLX130T Optional: Xilinx Virtex-6 XC6VLX240T, or XC6VSX315T

#### Custom I/O

Option -104: Installs the PMC P14 connector with 20 LVDS pairs to the FPGA Option -105: Installs the XMC P16 connector configurable as one 8X or two 4X gigabit serial links to the FPGA

#### Memory

Option 150 or 160: Two 8 MB QDRII+ SRAM memory banks, 400 MHz DDR **Option 155 or 165:** Two 512 MB DDR3 SDRAM memory banks. 400 MHz DDR

## **PCI-Express Interface**

PCI Express Bus: Gen. 1 x4 or x8; Gen. 2: x4

#### **Environmental**

Operating Temp: 0° to 50° C Storage Temp: -20° to 90° C

Relative Humidity: 0 to 95%, non-cond. Size: Standard XMC module, 2.91 in. x 5.87 in.

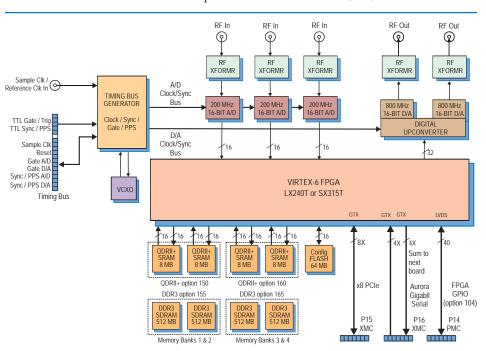

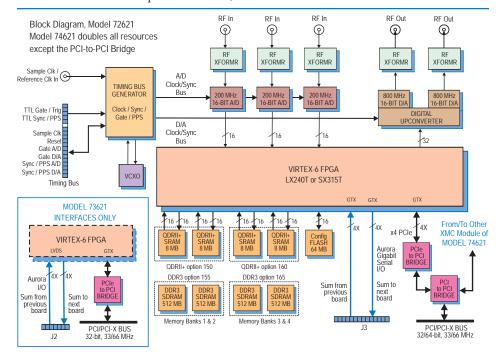

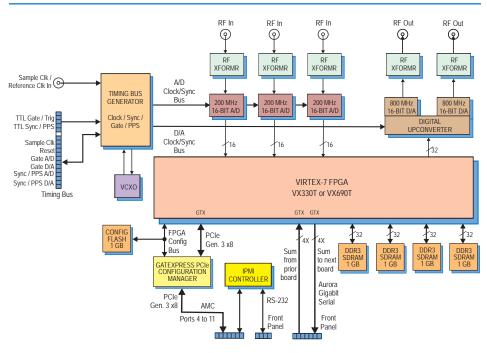

It includes three A/Ds, two D/As and four banks of memory. In addition to supporting PCI Express Gen. 2 as a native interface, the Model 71621 includes a general purpose connector for application-specific I/O.

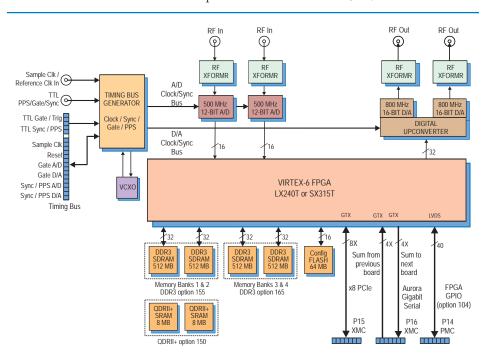

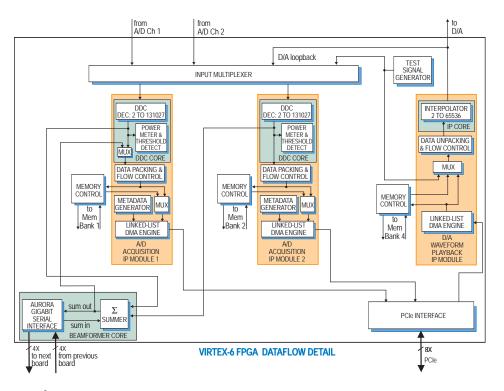

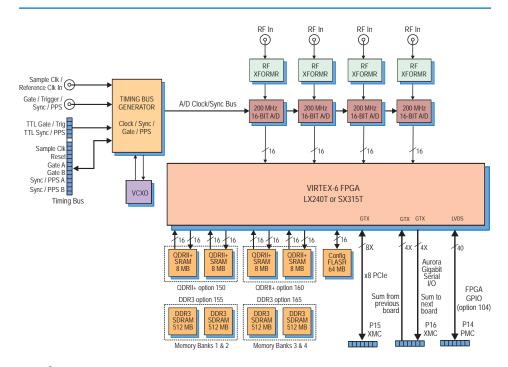

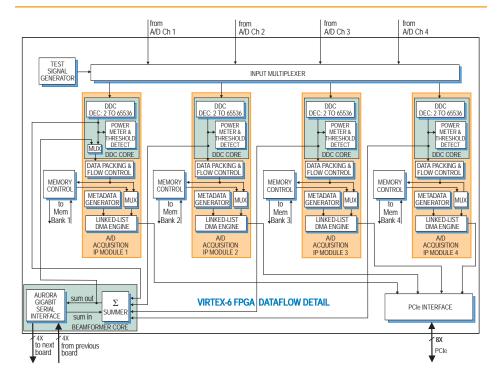

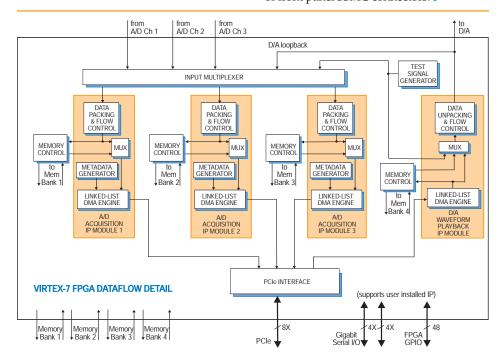

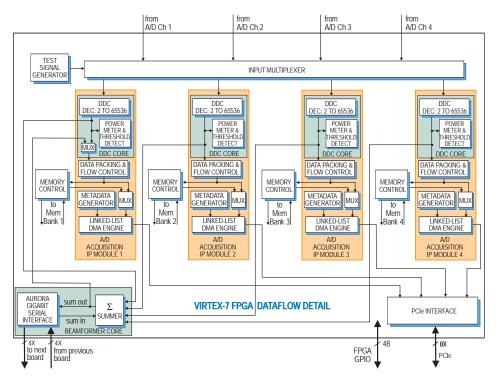

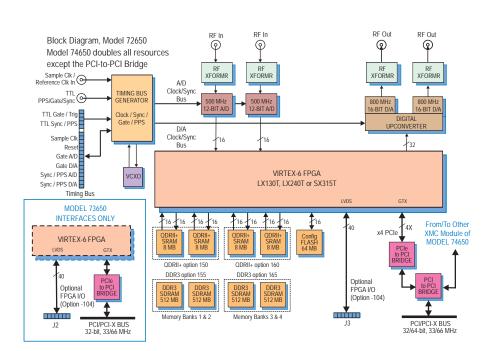

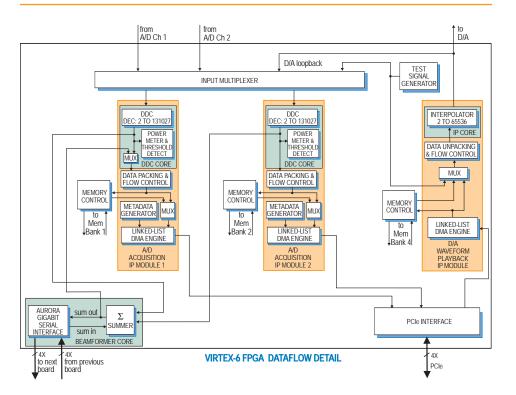

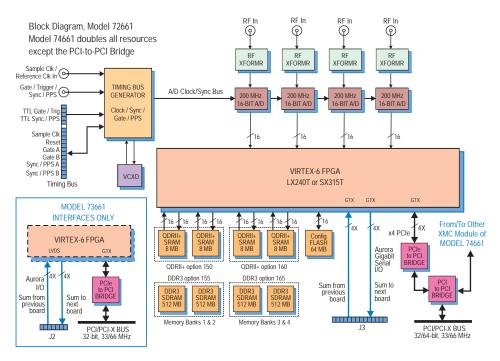

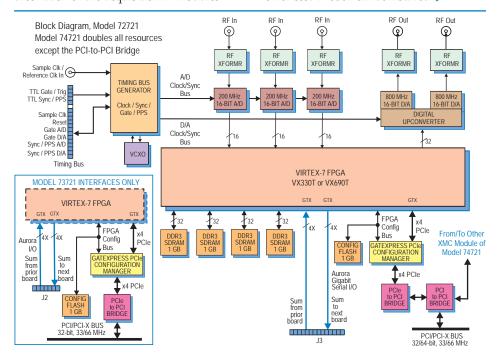

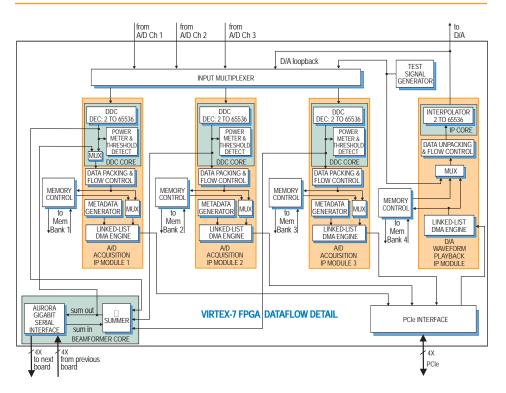

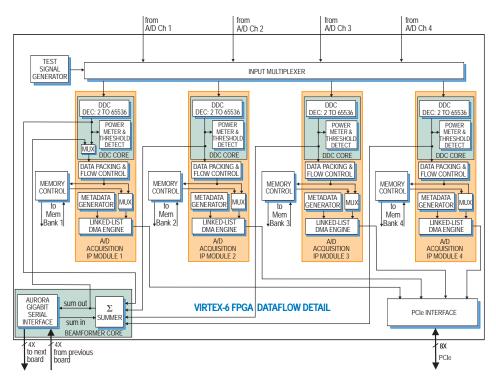

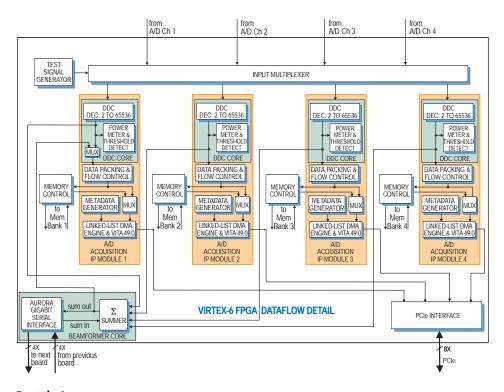

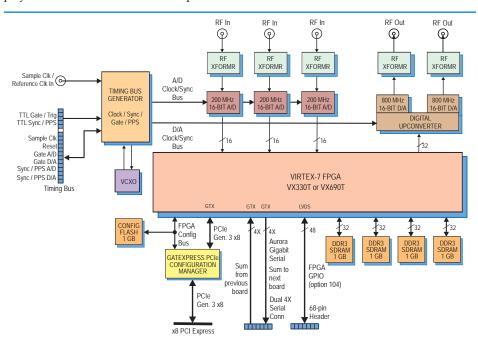

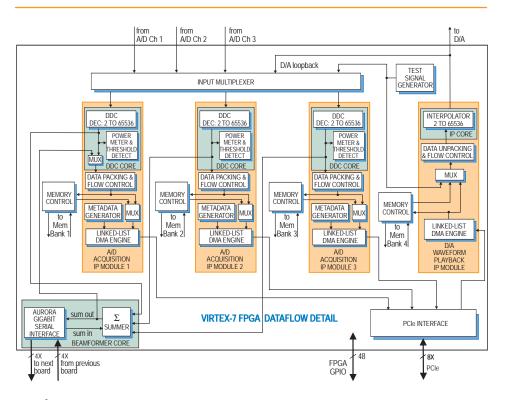

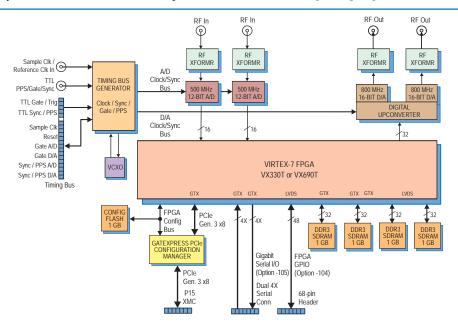

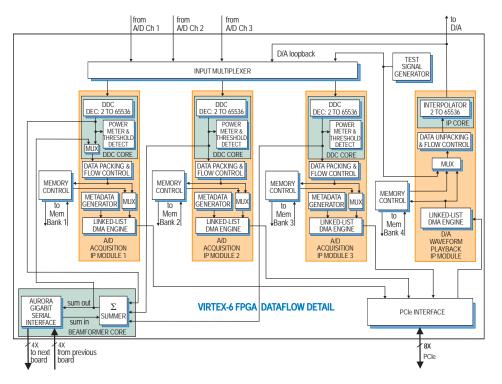

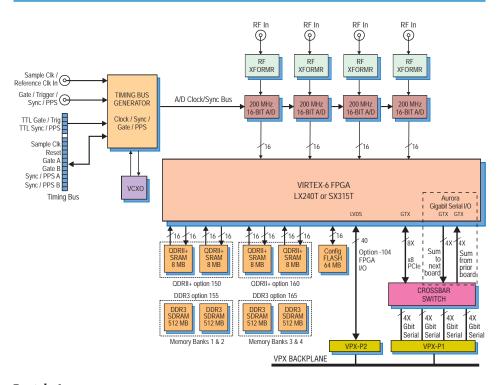

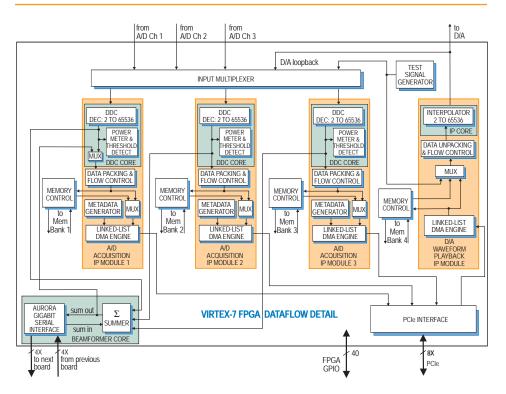

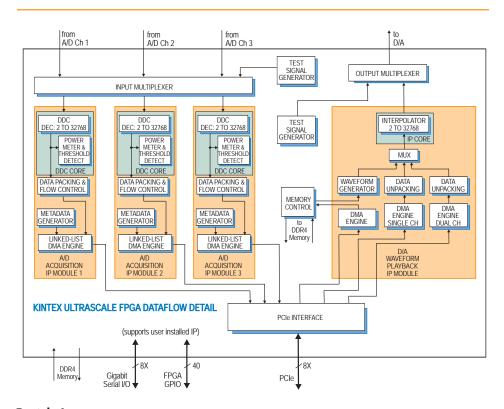

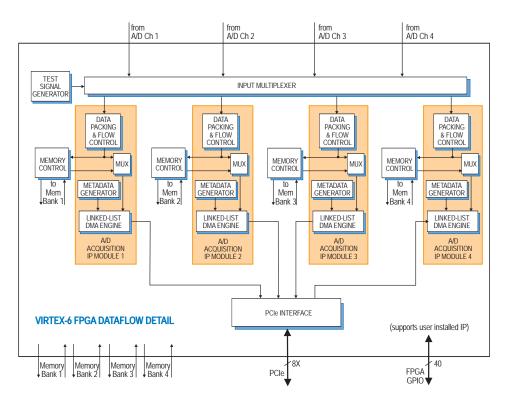

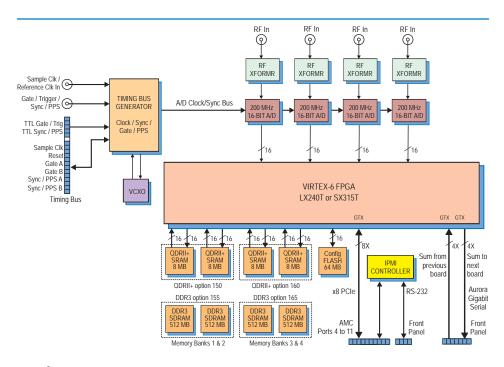

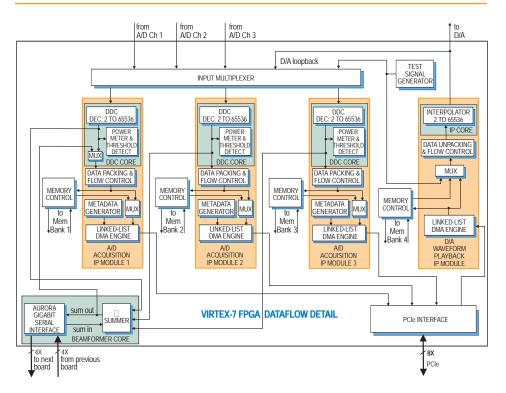

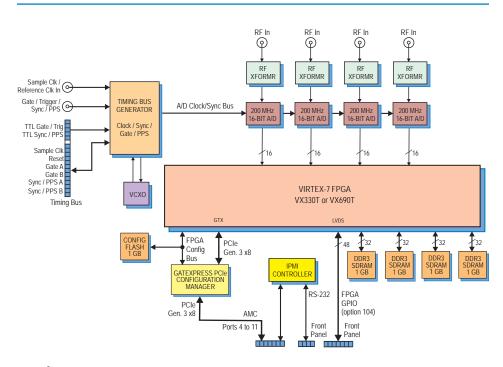

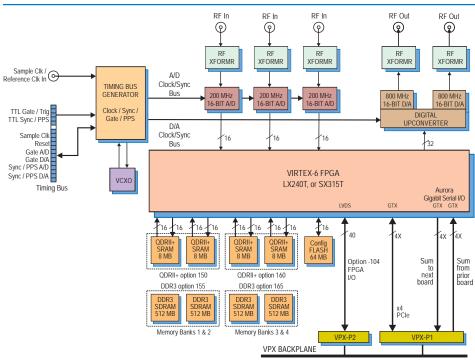

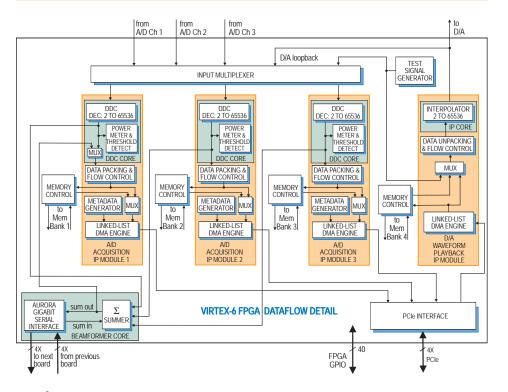

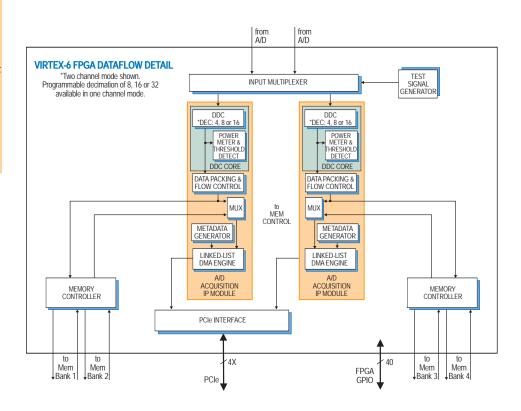

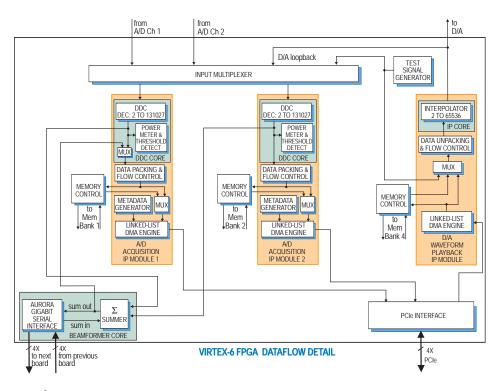

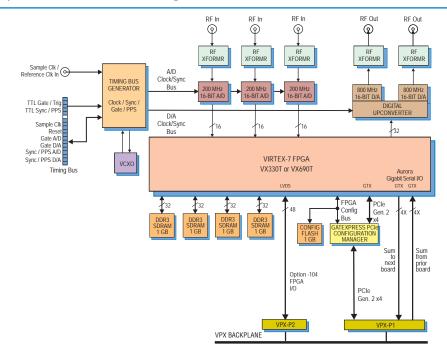

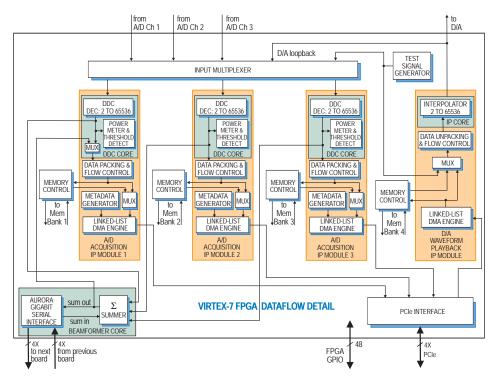

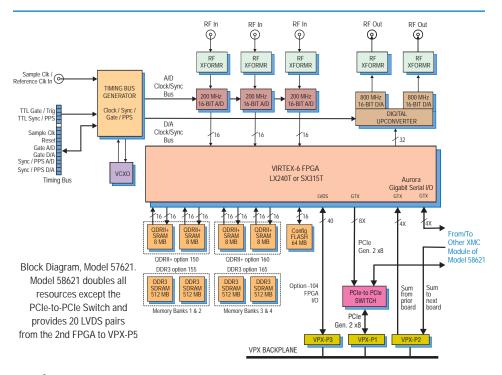

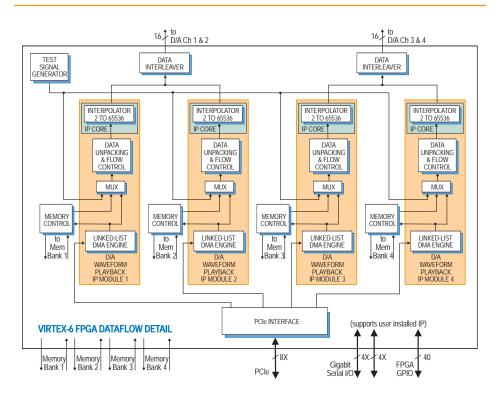

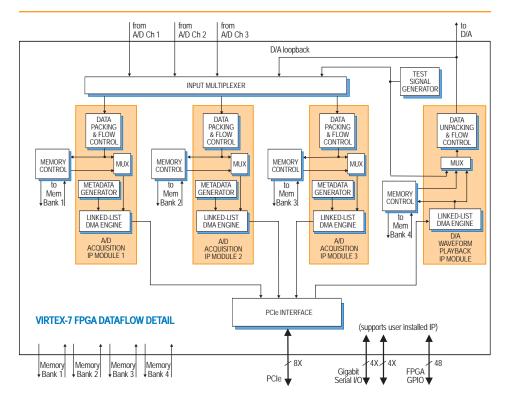

## **The Cobalt Architecture**

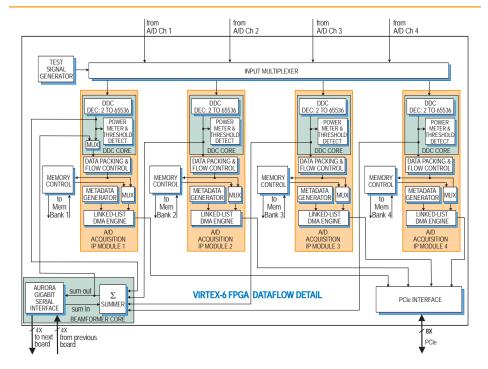

The Pentek Cobalt Architecture features a Virtex-6 FPGA. All of the board's data and control paths are accessible by the FPGA, enabling factory-installed functions including data multiplexing, channel selection, data packing, gating, triggering and memory control. The Cobalt Architecture organizes the FPGA as a container for data processing applications where each function exists as an intellectual property (IP) module.

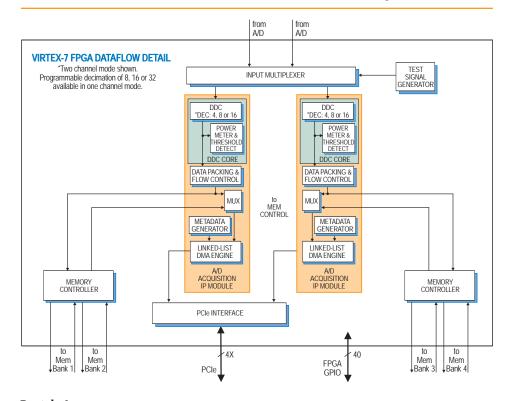

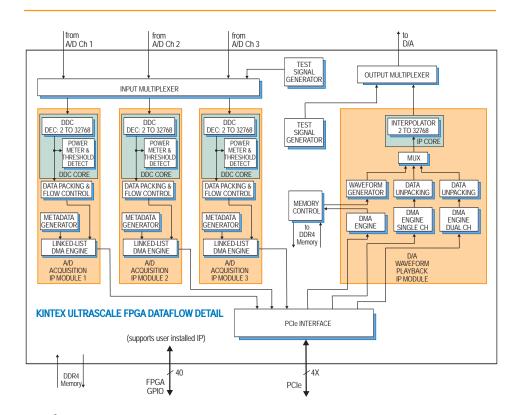

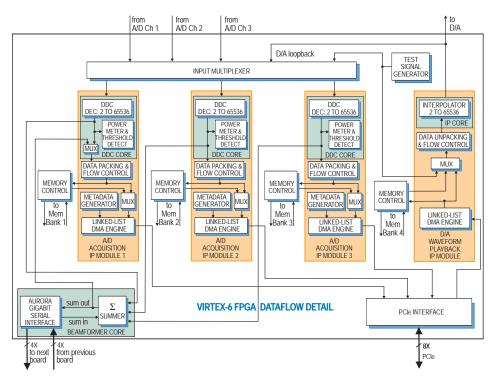

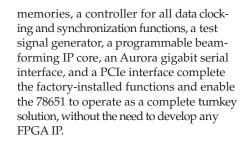

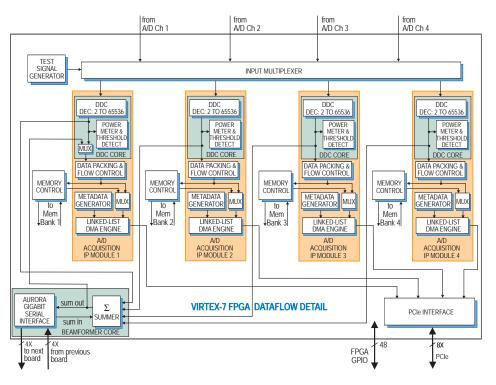

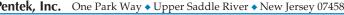

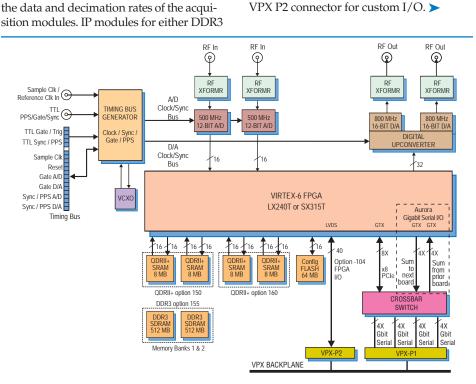

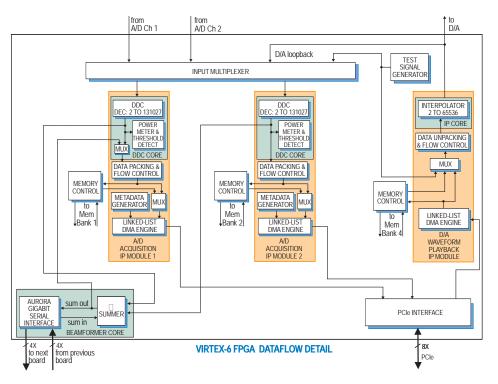

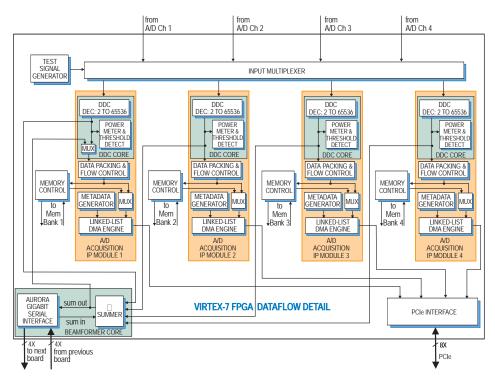

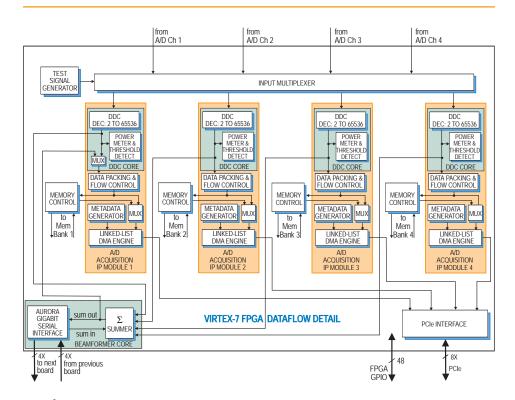

Each member of the Cobalt family is delivered with factory-installed applications ideally matched to the board's analog interfaces. The 71621 factory installed functions include three A/D acquisition and a D/A waveform playback IP modules. Each of the three acquisition IP modules contains a powerful, programmable DDC IP core. The waveform playback IP module contains an intrepolation IP core, ideal for matching playback rates to the data and decimation rates of the acqui-

sition modules. IP modules for either DDR3 or QDRII+ memories, a controller for all data clocking and synchronization functions, a test signal generator, a programmable beamforming IP core, an Aurora gigabit serial interface, and a PCIe interface complete the factory-installed functions and enable the 71621 to operate as a complete turnkey solution, without the need to develop any FPGA IP.

## **Extendable IP Design**

For applications that require specialized function, users can install their own custom IP for data processing. Pentek GateFlow FPGA Design Kits include all of the factory-installed modules as documented source code. Developers can integrate their own IP with the Pentek factory-installed functions or use the GateFlow kit to completely replace the Pentek IP with their own.

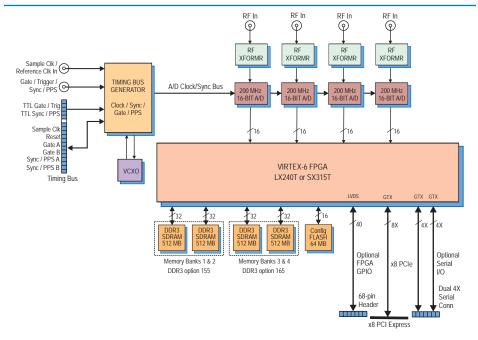

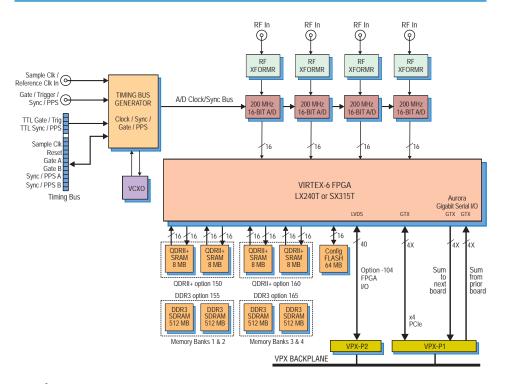

#### Xilinx Virtex-6 FPGA

The Virtex-6 FPGA site can be populated with two different FPGAs to match the specific requirements of the processing task. Supported FPGAs include: LX240T or SX315T. The SXT part features 1344 DSP48E slices and is ideal for modulation/demodulation, encoding/decoding, encryption/decryption, and channelization of the signals between transmission and reception. For applications not requiring large DSP resources, the lower-cost LXT FPGA can be installed.

Option -104 installs the P14 PMC connector with 20 pairs of LVDS connections to the FPGA for custom I/O.

#### **Features**

- Complete radar and software radio interface solution

- Supports Xilinx Virtex-6 LXT and SXT FPGAs

- Three 200 MHz 16-bit A/Ds

- Three multiband DDCs (digital downconverters)

- Two 800 MHz 16-bit D/As

- One DUC (digital upconverter)

- Multiboard programmable beamformer

- Up to 2 GB of DDR3 SDRAM or 32 MB of QDRII+ SRAM

- Sample clock synchronization to an external system reference

- LVPECL clock/sync bus for multimodule synchronization

- PCI Express (Gen. 1 & 2) interface up to x8

- Optional LVDS connections to the Virtex-6 FPGA for custom I/O

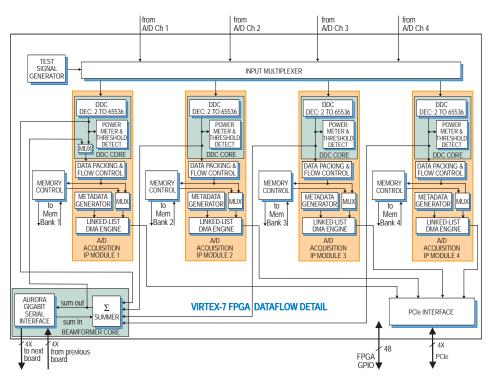

## A/D Acquisition IP Modules

The 71621 features three A/D Acquisition IP Modules for easily capturing and moving data. Each module can receive data from any of the three A/Ds, a test signal generator or from the D/A Waveform Playback IP Module in loopback mode.

Each IP module has an associated memory bank for buffering data in FIFO mode or for storing data in transient capture mode. All memory banks are supported with DMA engines for easily moving A/D data through the PCIe interface.

These powerful linked-list DMA engines are capable of a unique Acquisition Gate Driven mode. In this mode, the length of a transfer performed by a link definition need not be known prior to data acquisition; rather, it is governed by the length of the acquisition gate. This is extremely useful in applications where an external gate drives acquisition and the exact length of that gate is not known or is likely to vary.

For each transfer, the DMA engine can automatically construct metadata packets containing A/D channel ID, a sample-accurate time stamp and data length information. These actions simplify the host processor's job of identifying and executing on the data.

#### **DDC IP Cores**

Within each A/D Acquisition IP Module is a powerful DDC IP core. Because of the flexible input routing of the A/D Acquisition IP Modules, many different configurations can be achieved including one A/D driving all three DDCs or each of the three A/Ds driving its own DDC.

Each DDC has an independent 32-bit tuning frequency setting that ranges from DC to

$f_{\rm s}$ , where  $f_{\rm s}$  is the A/D sampling frequency. Each DDC can have its own unique decimation setting, supporting as many as three different output bandwidths for the board. Decimations can be programmed from 2 to 65,536 providing a wide range to satisfy most applications.

The decimating filter for each DDC accepts a unique set of user-supplied 18-bit coefficients. The 80% default filters deliver an output bandwidth of  $0.8*f_{\rm s}/{\rm N}$ , where N is the decimation setting. The rejection of adjacent-band components within the 80% output bandwidth is better than 100 dB. Each DDC delivers a complex output stream consisting of 24-bit I + 24-bit Q or16-bit I + 16-bit Q samples at a rate of  $f_{\rm s}/{\rm N}$ .

#### **Beamformer IP Core**

In addition to the DDCs, the 71621 features a complete beamforming subsystem. Each DDC core contains programable I & Q phase and gain adjustments followed by a power meter that continuously measures the individual average power output. The time constant of the averaging interval for each meter is programmable up to 8K samples. The power meters present average power measurements for each DDC core output in easy-to-read registers.

In addition, each DDC core includes a threshold detector to automatically send an interrupt to the processor if the average

power level of any DDC core falls below or exceeds a programmable threshold.

A programmable summation block provides summing of any of the three DDC core outputs. An additional programmable gain stage compensates for summation change bit growth. A power meter and threshold detect block is provided for the summed output. The output is then directed back into the A/D Acquisition IP Module 1 FIFO for reading over the PCIe. For larger systems, multiple 71621's can be chained together via a built-in Xilinx Aurora gigabit serial interface through the P16 XMC connector. This allows summation across channels on multiple boards.

## D/A Waveform Playback IP Module

The Model 71621 factory-installed functions include a sophisticated D/A Waveform Playback IP module. A linked-list controller allows users to easily play back to the dual D/As waveforms stored in either on-board memory or off-board host memory .

Parameters including length of waveform, delay from playback trigger, waveform repetition, etc. can be programmed for each waveform.

Up to 64 individual link entries can be chained together to create complex waveforms with a minimum of programming. >

### ➤ A/D Converter Stage

The front end accepts three analog HF or IF inputs on front panel SSMC connectors with transformer coupling into three Texas Instruments ADS5485 200 MHz, 16-bit A/D converters.

The digital outputs are delivered into the Virtex-6 FPGA for signal processing, data capture and for routing to other module resources.

## Digital Upconverter and D/A Stage

A TI DAC5688 DUC (digital upconverter) and D/A accepts a baseband real or complex data stream from the FPGA and provides that input to the upconvert, interpolate and dual D/A stages.

When operating as a DUC, it interpolates and translates real or complex baseband input signals to any IF center frequency up to 360 MHz. It delivers real or quadrature (I+Q) analog outputs to the dual 16-bit D/A converter. Analog output is through a pair of front panel SSMC connectors.

If translation is disabled, the DAC5688 acts as a dual interpolating 16-bit D/A with output sampling rates up to 800 MHz. In both modes the DAC5688 provides interpolation factors of 2x, 4x and 8x. In addition to the DAC5688, an FPGA based interpolator core provides additional interpolation from 2x to 65,536x. The two interpolators can be combined to create a total range from 2x to 524,288x.

## **Clocking and Synchronization**

Two internal timing buses provide either a single clock or two different clock rates to the A/D and D/A signal paths.

Each timing bus includes a clock, sync and a gate or trigger signal. An on-board clock generator receives an external sample clock from the front panel SSMC connector. This clock can be used directly for either the A/D or D/A sections or can be divided by a built-in clock synthesizer circuit to provide different A/D and D/A clocks. In an alternate mode, the sample clock can be sourced from an on-board programmable VCXO (Voltage-Controlled Crystal Oscillator). In this mode, the front panel SSMC connector can be used to provide a 10 MHz reference clock for synchronizing the internal oscillator.

A front panel 26-pin LVPECL Clock/Sync connector allows multiple modules to be synchronized. In the slave mode, it accepts LVPECL inputs that drive the clock, sync and gate signals. In the master mode, the LVPECL bus can drive the timing signals for synchronizing multiple modules.

Multiple 71621's can be driven from the LVPECL bus master, supporting synchronous sampling and sync functions across all connected modules.

#### **Memory Resources**

The 71621 architecture supports up to four independent memory banks which can be configured with all QDRII+ SRAM, DDR3 SDRAM, or as combination of two banks of each type of memory.

Each QDRII+ SRAM bank can be up to 8 MB deep and is an integral part of the module's DMA capabilities, providing FIFO memory space for creating DMA packets. For applications requiring deep memory resources, DDR3 SDRAM banks can each be up to 512 MB deep. Built-in memory functions include an A/D data transient capture mode and D/A waveform playback mode.

In addition to the factory-installed functions, custom user-installed IP within the FPGA can take advantage of the memories for many other purposes.

#### **XMC Interface**

The Model 71621 complies with the VITA 42.0 XMC specification. Two connectors each provide dual 4X links or a single 8X link with up to a 6 GHz bit clock. With dual XMC connectors, the 71621 supports x8 PCIe on the first XMC connector. The second connector is used for the Aurora interface and provides a dedicated board-to board interface for beamforming accross multiple modules.

## **PCI Express Interface**

The Model 71621 includes an industrystandard interface fully compliant with PCI Express Gen. 1 & 2 bus specifications. Supporting PCIe links up to x8, the interface includes multiple DMA controllers for efficient transfers to and from the module.

## **Model 8266**

The Model 8266 is a fully-integrated PC development system for Pentek Cobalt, Onyx and Flexor PCI Express boards. It was created to save engineers and system integrators the time and expense associated with building and testing a development system that ensures optimum performance of Pentek boards.

## **Ordering Information**

Model Description

71621 3-Channel 200 MHz A/D with DDC, DUC with 2-Channel 800 MHz D/A, and a Virtex-6 FPGA -

XMC

#### Options:

| optiono. |                                                          |

|----------|----------------------------------------------------------|

| -062     | XC6VLX240T                                               |

| -064     | XC6VSX315T                                               |

| -104     | LVDS FPGA I/O through P14 connector                      |

| -150     | Two 8 MB QDRII+ SRAM<br>Memory Banks<br>(Banks 1 and 2)  |

| -160     | Two 8 MB QDRII+ SRAM<br>Memory Banks<br>(Banks 3 and 4)  |

| -155     | Two 512 MB DDR3<br>SDRAM Memory Banks<br>(Banks 1 and 2) |

| -165     | Two 512 MB DDR3<br>SDRAM Memory Banks<br>(Banks 3 and 4) |

Contact Pentek for availability of rugged and conduction-cooled versions

Model Description

8266 PC Development System See 8266 Datasheet for Options

### **➤** Specifications

Front Panel Analog Signal Inputs

Input Type: Transformer-coupled, front panel female SSMC connectors Transformer Type: Coil Craft WBC4-6TLB

**Full Scale Input:** +8 dBm into 50 ohms **3 dB Passband:** 300 kHz to 700 MHz

A/D Converters

Type: Texas Instruments ADS5485 Sampling Rate: 10 MHz to 200 MHz Resolution: 16 bits

**Digital Downconverters**

Quantity: Three channels

**Decimation Range:** 2x to 65,536x in two stages of 2x to 256x

**LO Tuning Freq. Resolution:** 32 bits, 0 to  $f_s$

**LO SFDR:** >120 dB

Phase Offset Resolution: 32 bits,

0 to 360 degrees

FIR Filter: 18-bit coefficients, 24-bit output, with user programmable coefficients

Default Filter Set: 80% bandwidth, <0.3

dB passband ripple, >100 dB stopband attenuation

#### D/A Converters

Type: Texas Instruments DAC5688

Input Data Rate: 250 MHz max.

Output IF: DC to 400 MHz max.

Output Signal: 2-channel real or

1-channel with frequency translation

Output Sampling Rate: 800 MHz max.

with 2x, 4x or 8x interpolation

**Resolution:** 16 bits **Digital Interpolator**

**Interpolation Range:** 2x to 65,536x in two stages of 2x to 256x

#### Beamformer

Summation: Three channels on-board; multiple boards can be summed via Summation Expansion Chain: One chain in and one chain out link via XMC connector using Aurora protocol Phase Shift Coefficients: I & Q with 16-bit resolution

Gain Coefficients: 16-bit resolution Channel Summation: 24-bit Multiboard Summation Expansion: 32-bit

#### Front Panel Analog Signal Outputs

Output: Transformer-coupled, front panel female SSMC connectors Transformer: Coil Craft WBC4-6TLB Full Scale Output: +4 dBm into 50 ohms 3 dB Passband: 300 kHz to 700 MHz

Sample Clock Sources: On-board clock synthesizer generates two clocks: one A/D clock and one D/A clock

#### **Clock Synthesizer**

Clock Source: Selectable from on-board programmable VCXO (10 to 810 MHz), front panel external clock or LVPECL timing bus

**Synchronization:** VCXO can be locked to an external 4 to 180 MHz PLL system reference, typically 10 MHz

Clock Dividers: External clock or VCXO can be divided by 1, 2, 4, 8, or 16, independently for the A/D clock and D/A clock

#### **External Clock**

**Type:** Front panel female SSMC connector, sine wave, 0 to +10 dBm, AC-coupled, 50 ohms, accepts 10 to 800 MHz divider input clock or PLL system reference

Timing Bus: 26-pin connector LVPECL bus includes, clock/sync/gate/PPS inputs and outputs; TTL signal for gate/ trigger and sync/PPS inputs

#### Field Programmable Gate Array

Standard: Xilinx Virtex-6 XC6VLX240T Optional: Xilinx Virtex-6 XC6VSX315T

#### Custom I/O

**Option -104:** Installs the PMC P14 connector with 20 LVDS pairs to the FPGA

#### Memory

Option 150 or 160: Two 8 MB QDRII+ SRAM memory banks, 400 MHz DDR Option 155 or 165: Two 512 MB DDR3 SDRAM memory banks, 400 MHz DDR

#### **PCI-Express Interface**

PCI Express Bus: Gen. 1: x4 or x8; Gen. 2: x4

## Environmental

Operating Temp: 0° to 50° C Storage Temp: -20° to 90° C

**Relative Humidity:** 0 to 95%, non-cond. **Size:** Standard XMC module, 2.91 in. x 5.87 in.

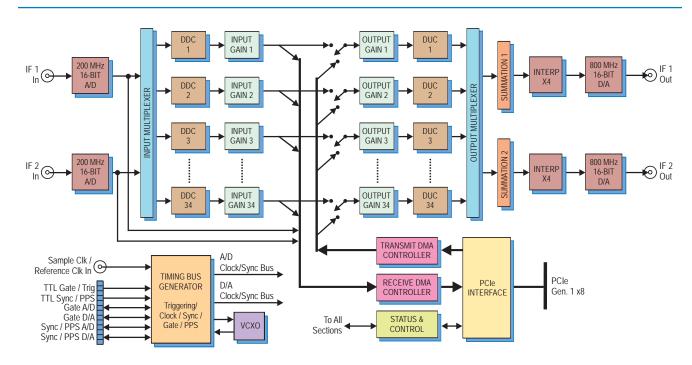

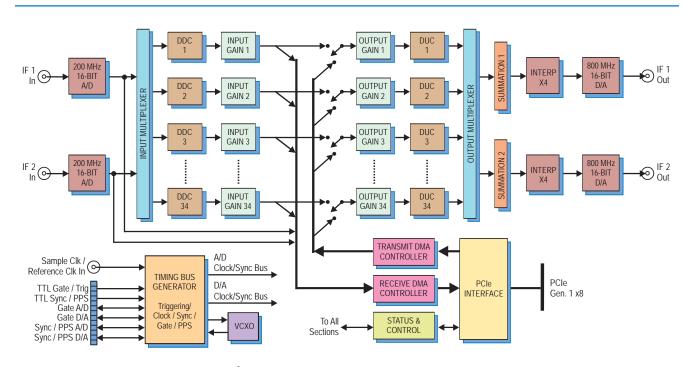

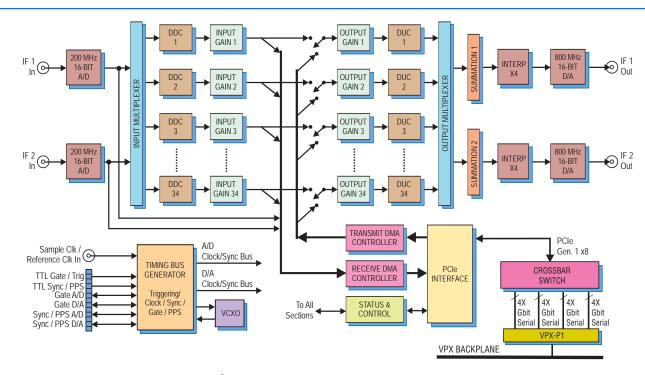

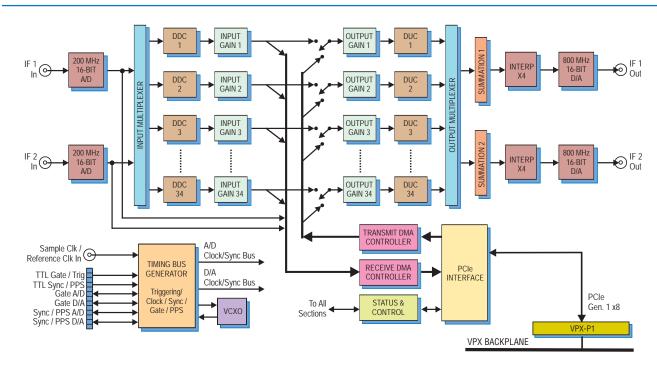

#### **Features**

- Modifies 34 IF signals between input and output

- Up to 80 MHz IF bandwidth

- Two 200 MHz 16-bit A/Ds

- Two 800 MHz 16-bit D/As

- 34 DDCs and 34 DUCs (digital downconverters and digital upconverters)

- Signal drop/add/replace

- Frequency shifting and hopping

- Amplitude boost and attenutation

- PCI Express Gen. 1: x4 or x8

#### **General Information**

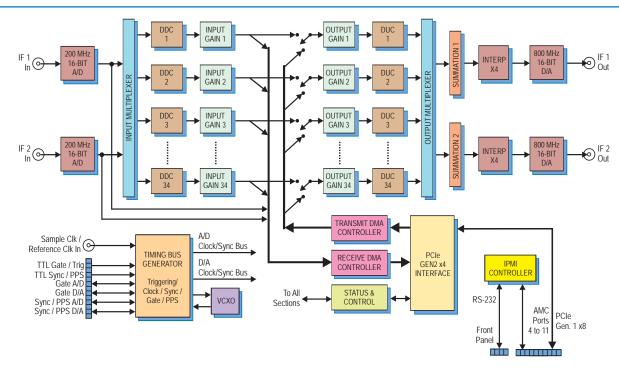

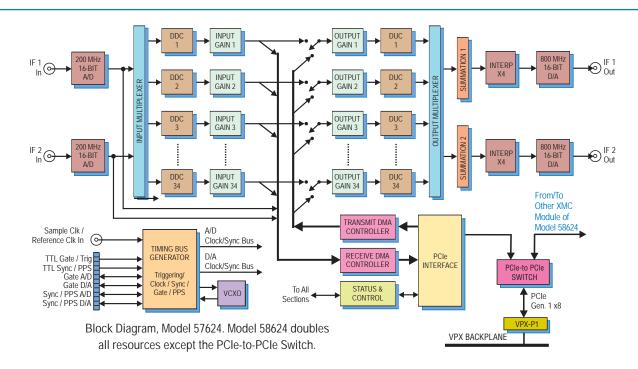

Model 71624 is a member of the Cobalt® family of high-performance XMC modules based on the Xilinx Virtex-6 FPGA. As an IF relay, it accepts two IF analog input channels, modifies up to 34 signals, and then delivers them to two analog IF outputs. Any signal within each IF band can be independently enabled or disabled, and changed in both frequency and amplitude as it passes through the module.

The 71624 supports many useful functions for both commercial and military communications systems including signal drop/add/replace, frequency shifting and hopping, amplitude equalization, and bandwidth consolidation. Applications include countermeasures, active tracking and monitoring, channel security, interception, adaptive spectral management, jamming, and encryption.

The Pentek Cobalt product family features the Virtex-6 FPGA. All of the board's data converters, interfaces and control lines are connected to the FPGA, which performs the data-routing and DSP functions for the adaptive relay.

A PCIe Gen. 1 system interface supports control, status and data transfers.

## **Adaptive Relay Input Overview**

The Model 71624 digitizes two analog IF inputs using two 200 MHz 16-bit A/D converters. The bandwidth of each IF signal can be up to 80 MHz, and may contain multiple signals, each centered at a different frequency. An array of 34 DDCs (digital downconverters) can be independently

programmed to translate any signal to baseband and then bandlimit the signal as required. DDC tuning frequency is programmable from 0 Hz to the A/D sample rate. Output bandwidth is programmable from around 20 kHz to 312 kHz for a sample rate of 200 MHz. Each DDC can independently source IF data from either of the two A/Ds.

Baseband I+Q DDC outputs are scaled in a programmable gain/attenuation block before being delivered across the PCIe system interface to target memory, typically associated with a system processor. Here, the signals can be analyzed, classified, demodulated, decrypted or decoded, depending on the application.

Samples from each A/D converter can also be delivered across PCIe to system memory so that the processor can access wideband IF data. By performing an FFT, the processor can identify signals and then tune the DDCs accordingly.

## **Adaptive Relay Output Overview**

The Model 71624 output stage consists of 34 DUCs (digital upconverters) and two 800 MHz 16-bit D/A converters. Each DUC accepts baseband I+Q signals from either the local DDCs or from system memory.

DUC inputs are scaled in programmable gain/attenuation blocks similar to those in the input stage. Each DUC is independently programmable for data source selection (DDC or memory), upconvert tuning frequency and bandwidth (interpolation).

The translated DUC outputs are directed to either of two summation blocks, each

➤ associated with one of the two D/A converters using a final interpolation factor of x4. After conversion, the IF analog outputs of each D/A can contain signals from any combination of the 34 DUCs.

#### Xilinx Virtex-6 FPGA

The SX315T Virtex-6 FPGA with 1344 DSP48E engines is well suited for the demanding signal processing tasks required by the Model 71624 adaptive relay. Because of the complexity and proprietary nature of these functions, the FPGA cannot be extended or modified by the user.

#### **A/D Converters**

The front-end accepts two analog HF or IF inputs on front panel SSMC connectors with transformer-coupling into two Texas Instruments ADS5485 200 MHz, 16-bit A/D converters.

The digital outputs are delivered into the Virtex-6 FPGA for the data capture and all of the remaining adaptive relay signal processing operations.

## **Digital Downconverters**

Each of the FPGA-based DDCs has an independent mixer and local oscillator with a 32-bit tuning frequency setting that ranges from DC to  $f_s$ , where  $f_s$  is the A/D sampling frequency, nominally 200 MHz. An IF input signal can be downconverted to a complex (I+Q) signal centered at 0 Hz by setting the DDC tuning frequency to its center frequency.

The DDC output bandwidth is determined by its decimation setting, which is programmable from 512 to 8192 in steps of 8. Each DDC can have a different decimation, thereby supporting up to 34 different signal bandwidths.

The fixed 80% decimating output filters deliver an output bandwidth equal to  $0.8*f_{\rm s}/{\rm N}$ , where N is the decimation setting and  $f_{\rm s}$  is the A/D sample rate. The rejection of adjacent-band components within the 80% output bandwidth is better than 100 dB.

Each DDC delivers a complex output stream consisting of 16-bit I + 16-bit Q samples at a rate of  $f_s/N$ .

### **Input Gain Blocks**

Each DDC complex output is delivered through a complex gain stage where the baseband signal can be amplified or attenuated. Each input gain block, which is a complex digital multiplier, accepts a unique 16-bit binary gain coefficient in Q8.8 format (8 bits integer + 8 bits fractional). This results in

gain values ranging from approximately +48 dB to -48 dB.

#### **Receive DMA Controller**

Two output DMA engines deliver data across the PCIe interface into user-specified memory locations in PCIe target memory. DMA engine #1 can deliver either raw samples from A/D Ch 1 or channel-interleaved 24-bit I and Q baseband samples from the 34 DDCs. Data samples from each DDC can be independently enabled/disabled for output. DMA engine #2 can deliver raw samples from A/D Ch 2.

When a target memory buffer is filled, the 71624 issues an interrupt to the system processor and then begins filling an alternate buffer. In this way, the processor is always informed when and where data is available for retrieval. Packet headers identify the DDC and show the number of subsequent data samples.

#### **Transmit DMA Controller**

Each of the FPGA-based 34 DUCs interpolates complex (I+Q) baseband signals and translates them to the desired IF output center frequency.

The data source for each DUC can be independently selected from its corresponding DDC output, or from PCIe target memory buffers fetched by the transmit DMA controller, where header information steers the memory data to the appropriate DUC channel.

Like the receive DMA controllers, once a data buffer is emptied, the 71624 signals the processor with an interrupt and moves to the next assigned buffer to continue fetching data.

### **Output Gain Blocks**

The complex baseband input for each DUC complex output is delivered through a complex gain stage where the baseband signal can be amplified or attenuated.

Each of the output gain blocks accepts a unique 16-bit binary gain coefficient in Q8.8 format (8 bits integer + 8 bits fractional). This results in gain values ranging from approximately +48 dB to -48 dB.

#### **Digital Upconverters**

The interpolation filter increases the baseband input sample rate by an interpolation factor typically equal to the decimation factor of the corresponding DDC. This interpolation factor is programmable from 512 to 8192 in steps of 8. Using this strategy, the interpolation sample rate equals the A/D sample rate, nominally 200 MHz.

▶ A complex digital mixer upconverts the interpolated baseband signal to the desired IF output center frequency. This frequency is determined by a local oscillator programmable with a 32-bit integer from DC to  $f_{sr}$  where  $f_{s}$  is the interpolator output frequency, nominally 200 MHz.

Each of the DUCs can have an independent interpolation factor and tuning frequency. However, all DUC outputs sharing a common summation block must have the same sample rate.

#### **Summation Blocks**

Two summation blocks accept any combination of the upconverted DUC signals by setting an enable bit for each DUC's contribution. Each DUC output can be enabled for none, one or both of the summation blocks.

The summation blocks deliver only real output samples to the subsequent D/A converter stage.

#### **D/A Converters**

A TI DAC5688 dual-channel D/A accepts two summed upconverted data streams, one from each summation block, and operates in its non-translating dual, real baseband mode. Its built-in interpolation filter is typically set to x4 mode, boosting the summation output sample rate from a nominal 200 MHz to 800 MHz. This simplifies the output low pass reconstruction filtering requirements.

Two transformer-coupled analog IF outputs are delivered through a pair of front panel SSMC connectors.

## **Clocking and Synchronization**

Two internal timing buses provide either a single clock or two different clock rates to the A/D and D/A signal paths.

Each timing bus includes a clock, sync and a gate or trigger signal. An on-board clock generator receives an external sample clock from the front panel SSMC connector. This clock can be used directly for either the A/D or D/A sections or can be divided by a built-in clock synthesizer circuit to provide different A/D and D/A clocks.

In an alternate mode, the sample clock can be sourced from an on-board programmable VCXO (voltage-controlled crystal oscillator). In this mode, the front panel SSMC connector can be used to provide a 10 MHz reference clock to phase-lock the internal oscillator.

A front panel 26-pin LVPECL Clock/Sync connector allows multiple modules to be synchronized. In the slave mode, it accepts LVPECL inputs that drive the clock, sync and gate signals. In the master mode, the LVPECL bus can drive the timing signals for synchronizing multiple modules.

Multiple 71624's can be driven from the LVPECL bus master, supporting synchronous sampling and sync functions across all connected modules.

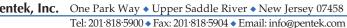

## **PCI Express XMC Interface**

The Model 71624 complies with the VITA 42.0 XMC specification. The primary XMC connector on P15 supports an industry-standard interface fully compliant with PCIe Gen. 1 x8, bus specifications. The interface automatically adjusts to accommodate fewer lanes, and includes dual DMA controllers for efficient transfers to and from the module.

## **Form Factor Adaptors**

All Pentek Cobalt XMC modules can be adapted to other standard embedded system form factors through the use of adaptor boards. Available versions include PCIe, 3U and 6U OpenVPX, 3U and 6U cPCI, and AMC. For more information and the Pentek's Product Selector Tool visit our website at: www.pentek.com.

## **Model 8266**

The Model 8266 is a fullyintegrated PC development system for Pentek Cobalt, Onyx and Flexor PCI Express boards. It was created to save engineers and system integrators the time and expense associated with building and testing a development system that ensures optimum performance of Pentek boards.

## **Ordering Information**

| Model | Description             |

|-------|-------------------------|

| 71624 | Dual-Channel 34-Signal  |

|       | Adaptive IF Relay - XMC |

#### Options:

| -064 | XC6VSX315T (required)  |

|------|------------------------|

| -702 | L2 (air cooled)        |

|      | environmental level    |

| -712 | L2 (conduction cooled) |

|      | environmental level    |

| -730 | 2-slot heatsink        |

Contact Pentek for availability of rugged and conduction-cooled versions

| Model | Description            |

|-------|------------------------|

| 8266  | PC Development System  |

|       | See 8266 Datasheet for |

|       | Options                |

### ➤ Specifications

Front Panel Analog Signal Inputs Input Type: Transformer-coupled, front panel female SSMC connectors Transformer Type: Coil Craft

WBC4-6TLB

Full Scale Input: +8 dBm into 50 ohms 3 dB Passband: 300 kHz to 700 MHz

#### A/D Converters

Quantity: 2

Type: Texas Instruments ADS5485 Sampling Rate: 10 MHz to 200 MHz

Resolution: 16 bits **Digital Downconverters**

**Ouantity: 34**

**Decimation Range:** 512 to 8192, in steps

LO Tuning Freq. Resolution: 32 bits,  $0 \text{ to } f_{s}$

**LO SFDR:** >100 dB

Phase Offset: 1 bit, 0 or 180 degrees

FIR Filter: 18-bit coefficients

Output: Complex, 16-bit I + 16-bit Q **Default Filter Set:** 80% bandwidth, <0.3 dB passband ripple, >100 dB stopband attenuation

## Input Gain Blocks

**Ouantity: 34**

Data: Complex, 16-bit I + 16-bit Q Gain Range: 16-bit Q8.8 format, approximately +/- 48 dB

## **Output Gain Blocks**

Quantity: 34

Data: Complex, 16-bit I + 16-bit Q Gain Range: 16-bit Q8.8 format, approximately +/-48 dB

#### **Digital Upconverters**

Quantity: 34

Interpolation Range: 512 to 8192, in

steps of 8

LO Tuning Freq. Resolution: 32 bits, 0 to  $f_s$

**LO SFDR:** >120 dB

FIR Filter: 18-bit coefficients, 16-bit output Default Filter Set: 80% bandwidth, <0.3 dB passband ripple, >100 dB stopband attenuation

## D/A Converters

**Analog Output Channels: 2 Type:** Texas Instruments DAC5688 **Input Data Rate:** 200 MHz max.

Output Signal: Real

Output Sampling Rate: 800 MHz max.

with 4x interpolation Resolution: 16 bits

## Front Panel Analog Signal Outputs

Output: Transformer-coupled, front panel female SSMC connectors Transformer: Coil Craft WBC4-6TLB Full Scale Output: +4 dBm into 50 ohms 3 dB Passband: 300 kHz to 700 MHz

Sample Clock Sources: On-board clock synthesizer generates two clocks: one A/D clock and one D/A clock

#### **Clock Synthesizer**

Clock Source: Selectable from on-board programmable VCXO (10 to 810 MHz), front panel external clock or LVPECL timing bus

Synchronization: VCXO can be locked to an external 4 to 180 MHz PLL system reference, typically 10 MHz

Clock Dividers: External clock or VCXO can be divided by 1, 2, 4, 8, or 16, independently for the A/D clock and D/A clock

#### **External Clock**

Type: Front panel female SSMC connector, sine wave, 0 to +10 dBm, AC-coupled, 50 ohms, accepts 10 to 800 MHz divider input clock or PLL system reference

Timing Bus: 26-pin connector LVPECL bus includes, clock/sync/gate/PPS inputs and outputs; TTL signal for gate/ trigger and sync/PPS inputs

## Field Programmable Gate Array

Required: Xilinx Virtex-6 XC6VSX315T

#### **PCI-Express Interface**

PCI Express Bus: Gen. 1: x4 or x8;

#### **Environmental**

Standard:

Operating Temp: 0° to 50° C **Storage Temp:** –20° to 90° C Relative Humidity: 0 to 95%, non-cond.

# Option 702 L2 Extended Temp (air-

Operating Temp: -20° to 65° C Storage Temp:  $-40^{\circ}$  to  $100^{\circ}$  C Relative Humidity: 0 to 95%, non-cond.

## Option 712 L2 Extended Temp (conduction-cooled):

Operating Temp: -20° to 65° C **Storage Temp:**  $-40^{\circ}$  to  $100^{\circ}$  C Relative Humidity: 0 to 95%, non-cond.

Size: Standard XMC module, 2.91 in. x 5.87 in.

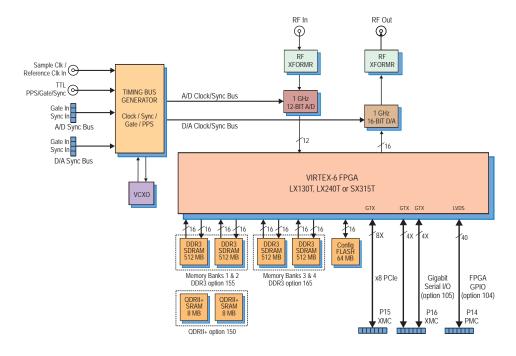

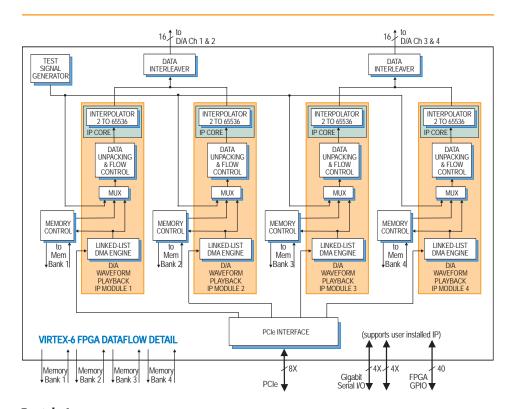

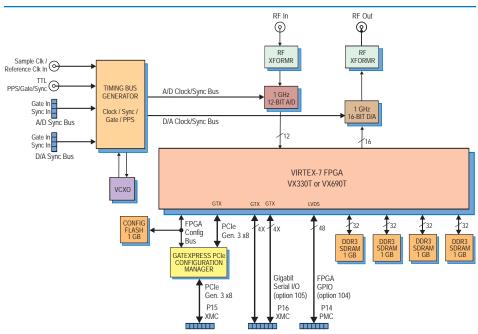

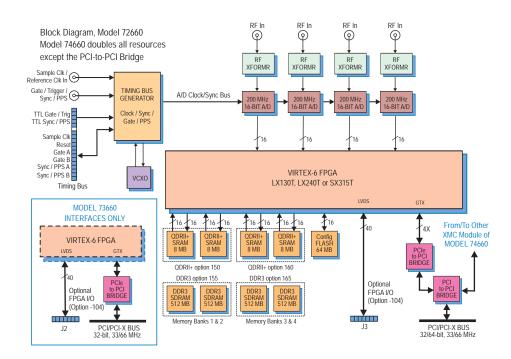

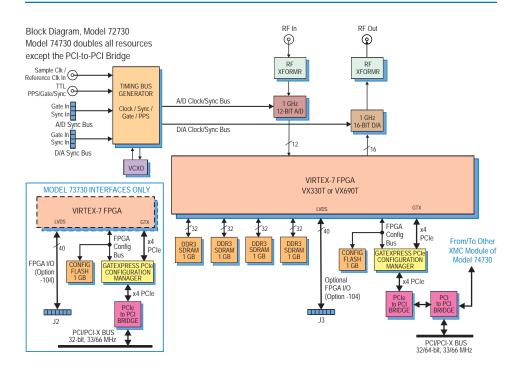

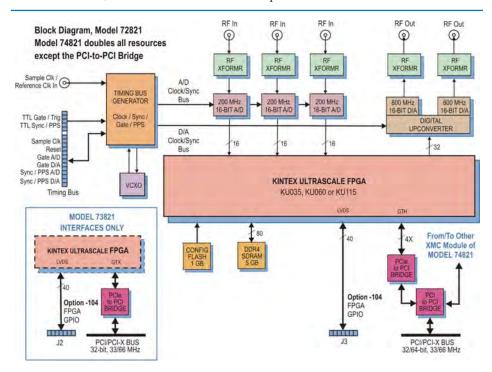

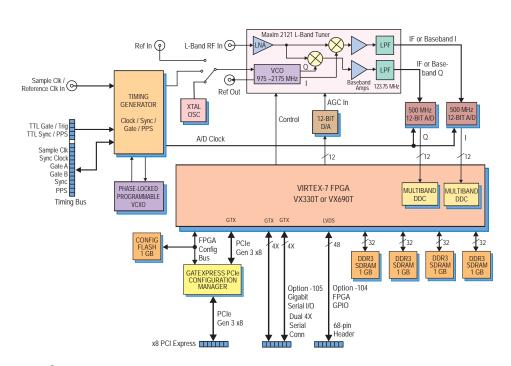

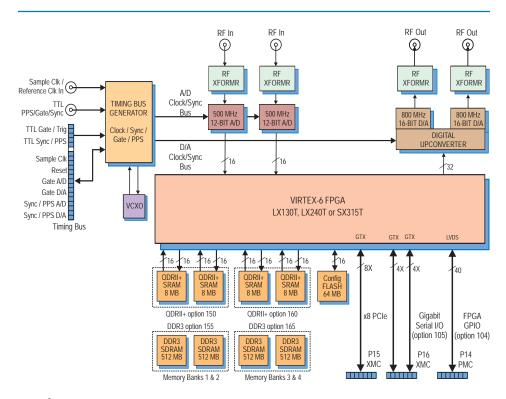

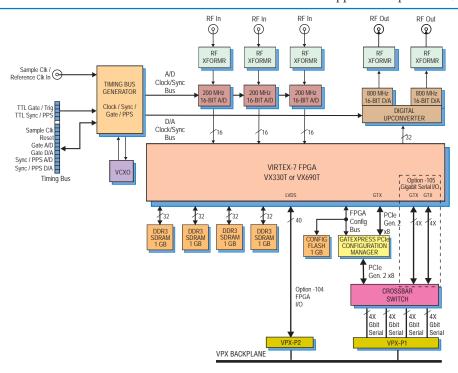

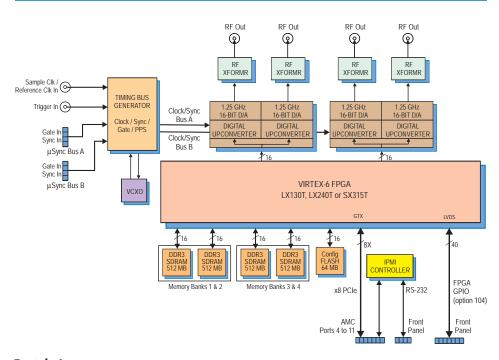

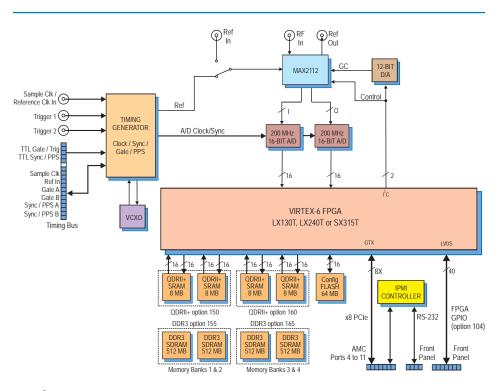

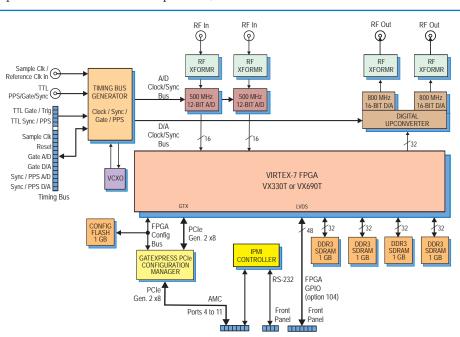

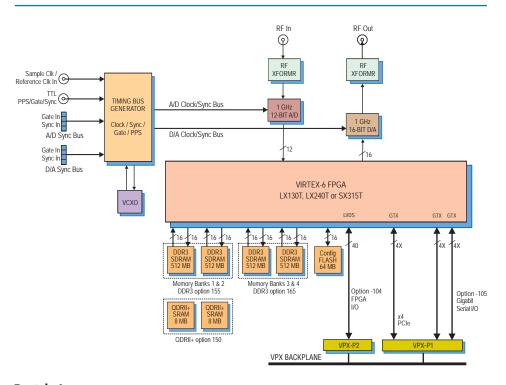

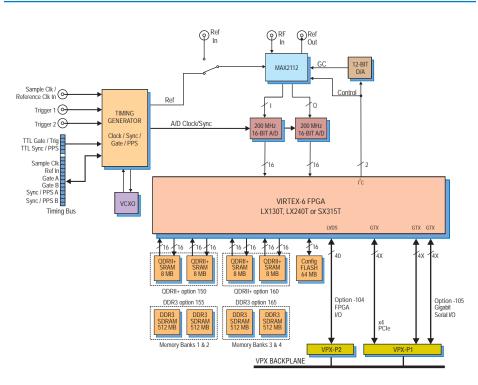

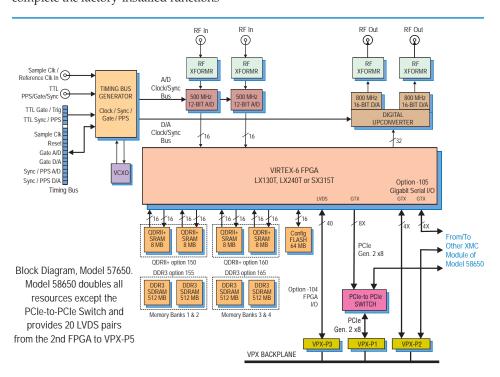

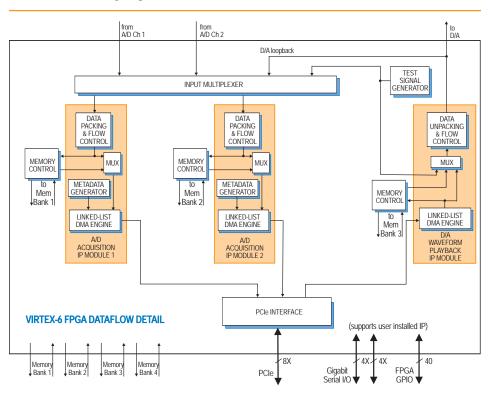

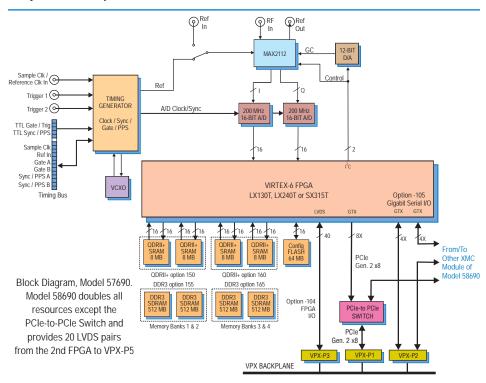

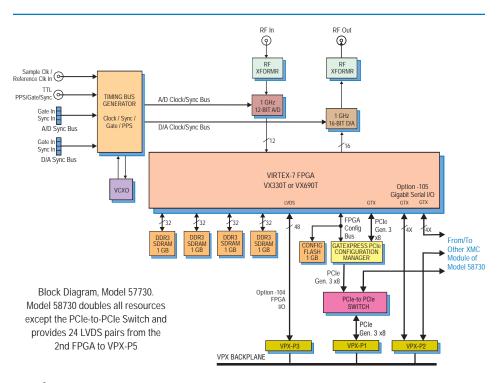

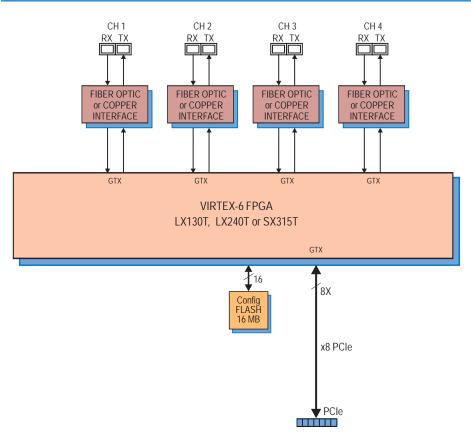

## 1 GHz A/D and 1 GHz D/A, Virtex-6 FPGA - XMC

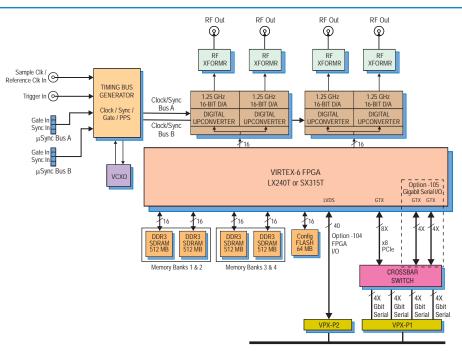

#### **Features**

- Complete radar and software radio interface solution

- Supports Xilinx Virtex-6 LXT and SXT FPGAs

- One 1 GHz 12-bit A/D

- One 1 GHz 16-bit D/A

- Up to 2 GB of DDR3 SDRAM or 16 MB of QDRII+ SRAM

- Sample clock synchronization to an external system reference

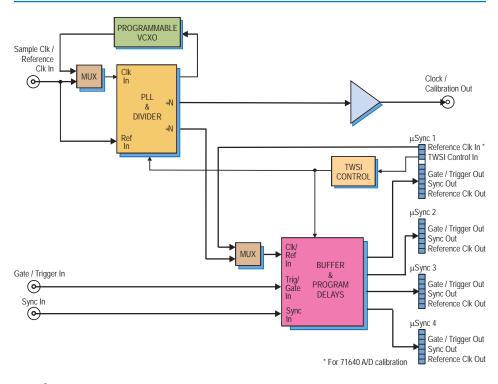

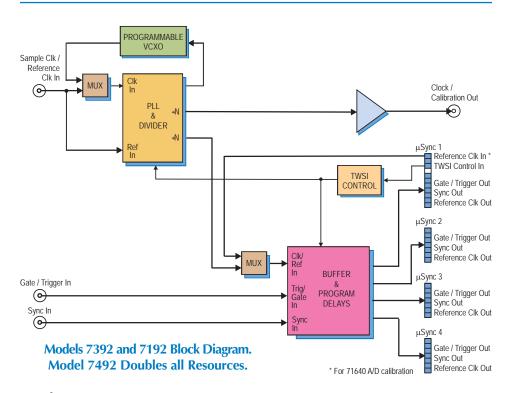

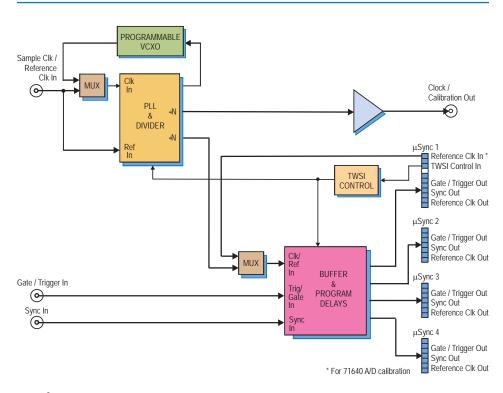

- Dual-µSync clock/sync bus for multimodule synchronization

- PCI Express (Gen. 1 & 2) interface up to x8

- Optional user-configurable gigabit serial interface

- Optional LVDS connections to the Virtex-6 FPGA for custom I/O

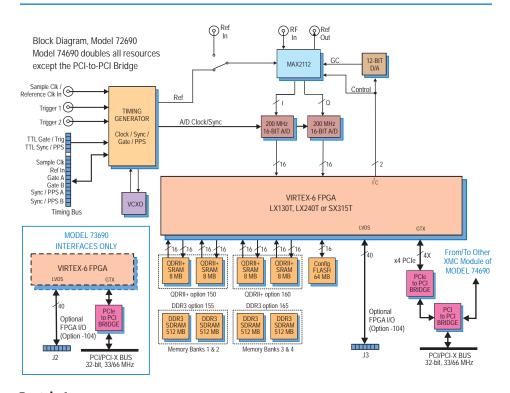

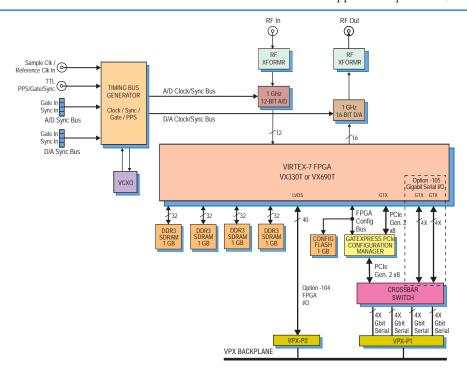

#### **General Information**

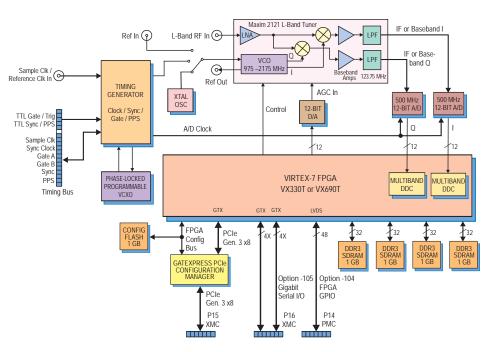

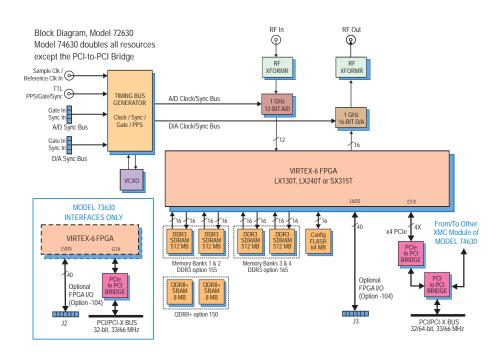

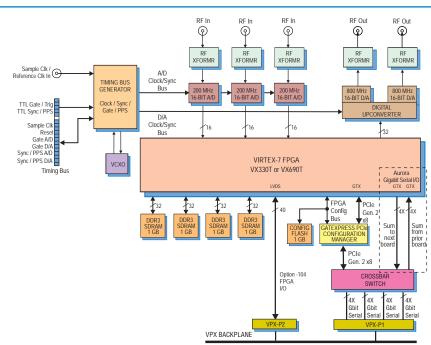

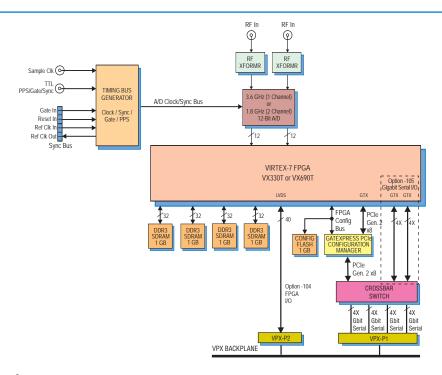

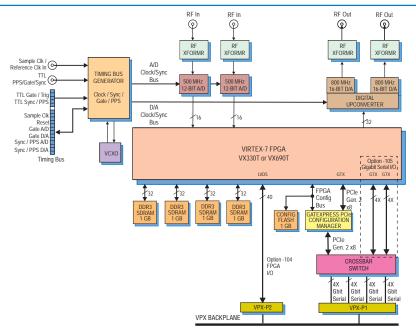

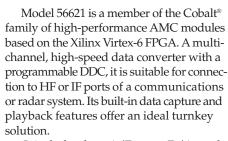

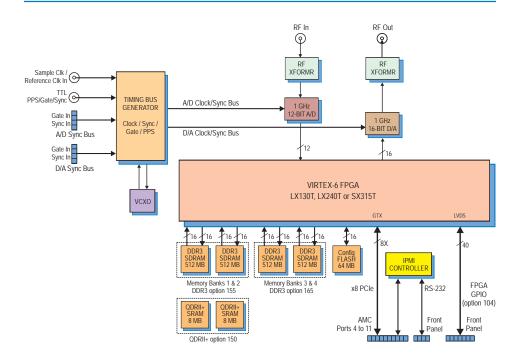

Model 71630 is a member of the Cobalt<sup>®</sup> family of high performance XMC modules based on the Xilinx Virtex-6 FPGA. A high-speed data converter, it is suitable for connection to HF or IF ports of a communications or radar system. Its built-in data capture and playback features offer an ideal turnkey solution as well as a platform for developing and deploying custom FPGA processing IP.

It includes 1 GHz A/D and D/A converters and four banks of memory. In addition to supporting PCI Express Gen. 2 as a native interface, the Model 71630 includes optional general purpose and gigabit serial card connectors for application-specific I/O.

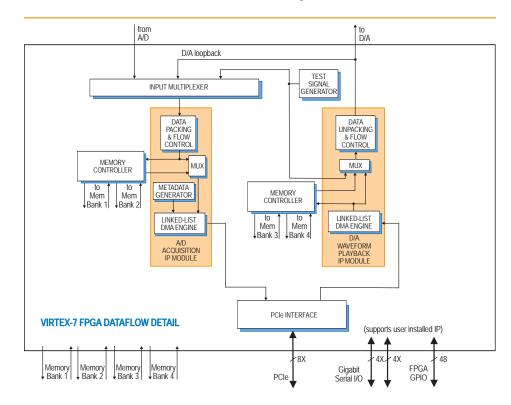

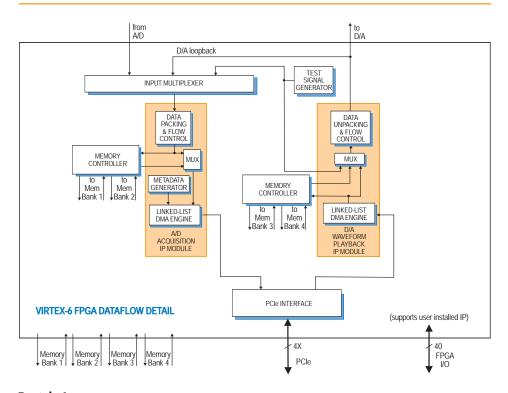

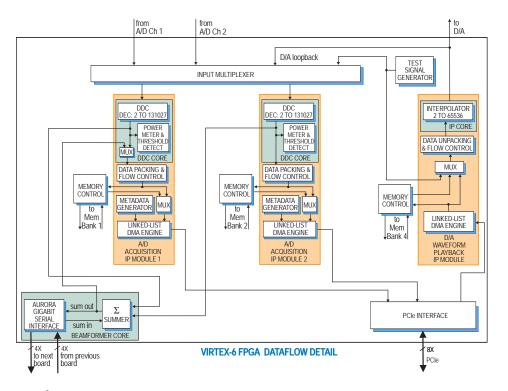

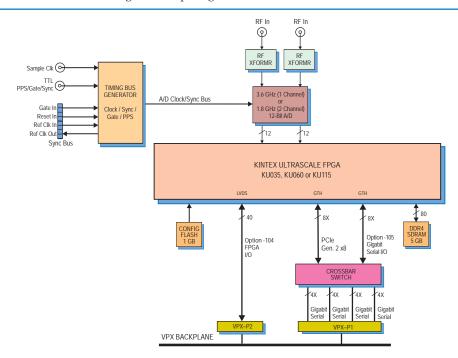

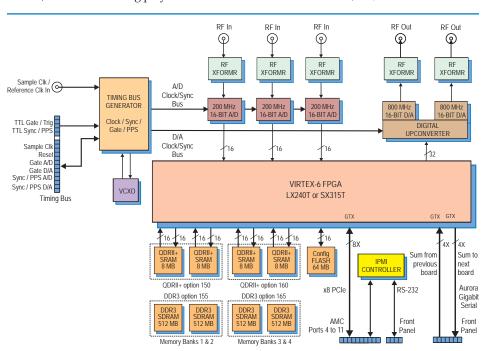

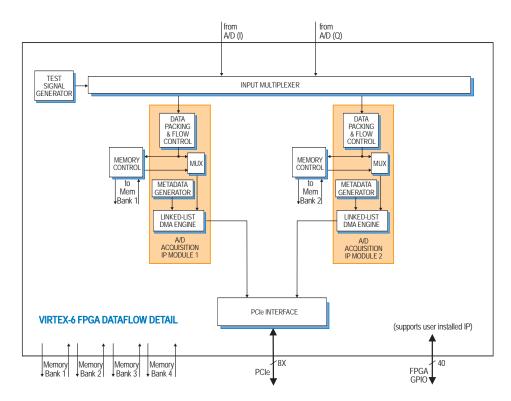

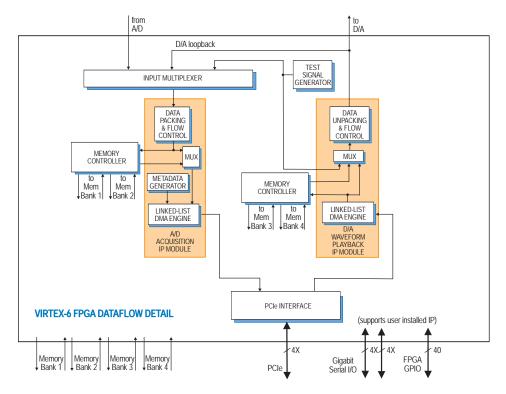

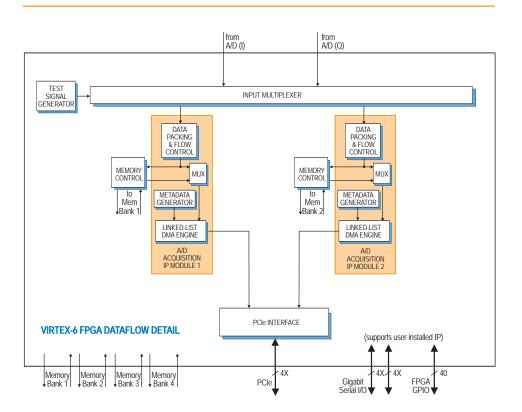

#### **The Cobalt Architecture**

The Pentek Cobalt architecture features a Virtex-6 FPGA. All of the board's data and control paths are accessible by the FPGA, enabling factory installed functions including data multiplexing, channel selection, data packing, gating, triggering and memory control. The Cobalt architecture organizes the FPGA as a container for data processing applications where each function exists as an intellectual property (IP) module.

Each member of the Cobalt family is delivered with factory-installed applications ideally matched to the board's analog interfaces. The 71630 factory-installed functions include an A/D acquisition and a D/A waveform playback IP module. In addition, IP modules for either DDR3 or QDRII+ memories, a controller for all data clocking and

synchronization functions, a test signal generator and a PCIe interface complete the factory-installed functions and enable the 71630 to operate as a complete turnkey solution, without the need to develop any FPGA IP.

## **Extendable IP Design**

For applications that require specialized functions, users can install their own custom IP for data processing. Pentek GateFlow FPGA Design Kits include all of the factory installed modules as documented source code. Developers can integrate their own IP with the Pentek factory-installed functions or use the GateFlow Design Kit to completely replace the Pentek IP with their own.

## **Xilinx Virtex-6 FPGA**

The Virtex-6 FPGA site can be populated with a variety of different FPGAs to match the specific requirements of the processing task. Supported FPGAs include: LX130T, LX240T, or SX315T. The SXT part features 1344 DSP48E slices and is ideal for modulation/demodulation, encoding/decoding, encryption/decryption, and channelization of the signals between transmission and reception. For applications not requiring large DSP resources, one of the lower-cost LXT FPGAs can be installed.

Option -104 installs the P14 PMC connector with 20 pairs of LVDS connections to the FPGA for custom I/O.

Option -105 installs the P16 XMC connector with one 8X or two 4X gigabit links to the FPGA to support serial protocols.

## 1 GHz A/D and 1 GHz D/A, Virtex-6 FPGA - XMC

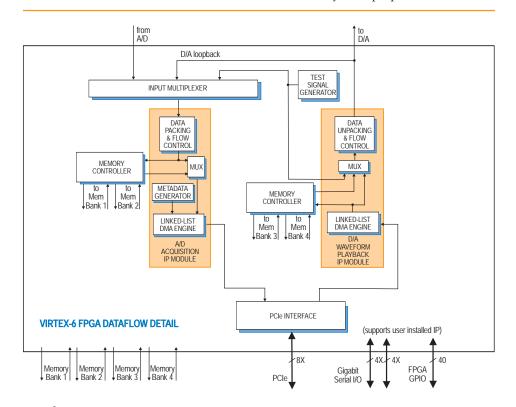

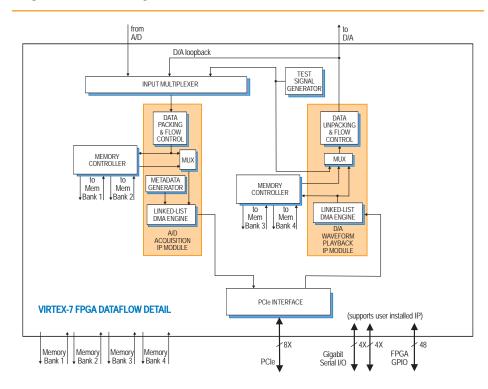

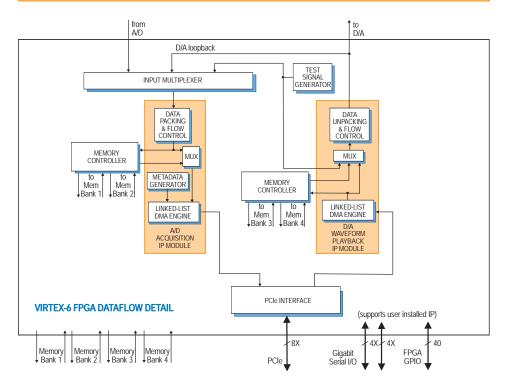

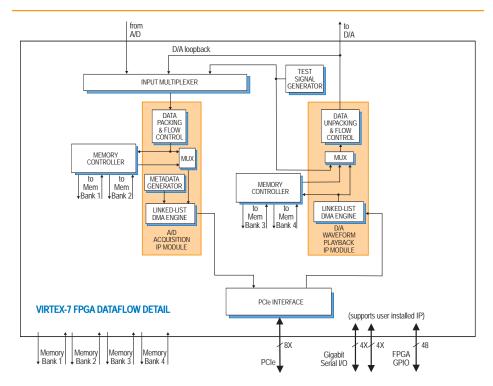

## A/D Acquisition IP Module

The 71630 features an A/D Acquisition IP Module for easy capture and data moving. The IP module can receive data from the A/D, a test signal generator, or from the D/A Waveform Playback IP Module in loopback mode. The IP module has associated memory banks for buffering data in FIFO mode or for storing data in transient capture mode. The memory banks are supported with a DMA engine for moving A/D data through the PCIe interface.

This powerful linked-list DMA engine is capable of a unique Acquisition Gate Driven mode. In this mode, the length of a transfer performed by a link definition need not be known prior to data acquisition; rather, it is governed by the length of the acquisition gate. This is extremely useful in applications where an external gate drives acquisition and the exact length of that gate is not known or is likely to vary.

For each transfer, the DMA engine can automatically construct metadata packets containing a sample-accurate time stamp, and data length information. These actions simplify the host processor's job of identifying and executing on the data.

# D/A Waveform Playback IP Module

The Model 71630 factory-installed functions include a sophisticated D/A Waveform Playback IP module. A linked-list controller allows users to easily play back waveforms stored in either on-board memory or off-board host memory to the D/A.

Parameters including length of waveform, delay from playback trigger, waveform repetition, etc. can be programmed for each waveform.

Up to 64 individual link entries can be chained together to create complex waveforms with a minimum of programming.

### ➤ A/D Converter Stage

The front end accepts an analog HF or IF input on a front panel SSMC connector with transformer coupling into a Texas Instruments ADS5400 1 GHz, 12-bit A/D converter.

The digital outputs are delivered into the Virtex-6 FPGA for signal processing, data capture or for routing to other module resources.

## D/A Converter Stage

The 71630 features a TI DAC5681Z 1 GHz, 16-bit D/A. The converter has an input sample rate of 1 GSPS, allowing it to acept full rate data from the FPGA. Additionally, the D/A includes a 2x or 4x interpolation filter for applications that provide 1/2 or 1/4 rate input data. Analog output is through a front panel SSMC connector.

## **Clocking and Synchronization**

Two internal timing buses provide either a single clock or two different clock rates to the A/D and D/A signal paths.

Each timing bus includes a clock, sync and a gate or trigger signal. An on-board clock generator receives a sample clock either from the front panel SSMC connector or from an on-board programmable VCXO (Voltage-Controlled Crystal Oscillator). In this latter mode, the front panel SSMC connector can be used to provide a 10 MHz reference clock to phase-lock the VCXO.

Either clock source (front panel or VCXO) can be used directly or can be divided independently by 2, 4, 8, or 16 to provide different lower frequency A/D and D/A clocks.

A pair of front panel  $\mu$ Sync connectors allows multiple modules to be synchronized. They accept CML inputs that drive the board's sync and gate/trigger signals.

The Pentek Model 7192 and Model 9192 Cobalt Synchronizers can drive multiple 71630  $\mu$ Sync connectors enabling large, multichannel synchronous configurations. Also, an LVTTL external gate/trigger input is accepted on a front panel SSMC connector.

## **Memory Resources**

The 71630 architecture supports up to four independent memory banks which can be configured with all QDRII+ SRAM, DDR3 SDRAM, or as combination of two banks of each type of memory. Each QDRII+ SRAM bank can be up to 8 MB deep and is an integral part of the module's DMA capabilities, providing FIFO memory space for creating DMA packets. For applications requiring deep memory resources, DDR3 SDRAM banks can each be up to 512 MB deep. Built-in memory functions include an A/D data transient capture mode and D/A waveform playback mode.

In addition to the factory-installed functions, custom user-installed IP within the FPGA can take advantage of the memories for many other purposes.

## **Model 8266**

The Model 8266 is a fully-integrated PC development system for Pentek Cobalt, Onyx and Flexor PCI Express boards. It was created to save engineers and system integrators the time and expense associated with building and testing a development system that ensures optimum performance of Pentek boards.

## **Ordering Information**

| Model | Description         |

|-------|---------------------|

| 71630 | 1 GHz A/D and D/A,  |

|       | Virtex-6 FPGA - XMC |

#### Options:

| -002* | -2 FPGA speed grade                                      |

|-------|----------------------------------------------------------|

| -062  | XC6VLX240T FPGA                                          |

| -064  | XC6VSX315T FPGA                                          |

| -104  | LVDS FPGA I/O through P14 connector                      |

| -105  | Gigabit serial FPGA I/O through P16 connector            |

| -150  | Two 8 MB QDRII+ SRAM<br>Memory Banks<br>(Banks 1 and 2)  |

| -155  | Two 512 MB DDR3<br>SDRAM Memory Banks<br>(Banks 1 and 2) |

| -165  | Two 512 MB DDR3<br>SDRAM Memory Banks<br>(Banks 3 and 4) |

\* This option is always required

Contact Pentek for availability of rugged and conduction-cooled versions

| Model | Description |

|-------|-------------|

|-------|-------------|

8266 PC Development System See 8266 Datasheet for Options

#### ➤ XMC Interface

The Model 71630 complies with the VITA 42.0 XMC specification. Two connectors each provide dual 4X links or a single 8X link with up to a 6 GHz bit clock. With dual XMC connectors, the 71630 supports x8 PCIe on the first XMC connector leaving the second connector free to support user-installed transfer protocols specific to the target application.

## **PCI Express Interface**

The Model 71630 includes an industrystandard interface fully compliant with PCI Express Gen. 1 & 2 bus specifications. Supporting PCIe links up to x8, the interface includes multiple DMA controllers for efficient transfers to and from the module.

## **Specifications**

## Front Panel Analog Signal Inputs

**Input Type:** Transformer-coupled, front panel female SSMC connectors

#### A/D Converter

Type: Texas Instruments ADS5400 Sampling Rate: 100 MHz to 1 GHz Resolution: 12 bits

#### D/A Converter

Type: Texas Instruments DAC5681Z Input Data Rate: 1 GHz max. Interpolation Filter: bypass, 2x or 4x Output Sampling Rate: 1 GHz max. Resolution: 16 bits

## Front Panel Analog Signal Outputs

Output Type: Transformer-coupled, front panel female SSMC connectors

**Sample Clock Sources:** On-board clock synthesizer generates two clocks: one A/D clock and one D/A clock

## Clock Synthesizer

Clock Source: Selectable from on-board programmable VCXO or front panel external clock

VCXO Frequency Ranges: 10 to 945 MHz, 970 to 1134 MHz, and 1213 to 1417 MHz

**Synchronization:** VCXO can be phase-locked to an external 4 to 200 MHz system reference, typically 10 MHz

Clock Dividers: External clock or VCXO can be divided by 1, 2, 4, 8, or 16, independently for the A/D clock and D/A clock

#### **External Clock**

Type: Front panel female SSMC connector, sine wave, 0 to +10 dBm, AC-coupled, 50 ohms, accepts 100 MHz to 1 GHz divider input clock, or PLL system reference

Timing Bus: 19-pin µSync bus connector includes sync and gate/trigger inputs, CMI.

#### **External Trigger Input**

**Type:** Front panel female SSMC connector, LVTTL

**Function:** Programmable functions include: trigger, gate, sync and PPS

#### Field Programmable Gate Array

Standard: Xilinx Virtex-6 XC6VLX130T-2 Optional: Xilinx Virtex-6 XC6VLX240T-2 or XC6VSX315T-2

#### Custom I/O

**Option -104:** Installs the PMC P14 connector with 20 LVDS pairs to the FPGA **Option -105:** Installs the XMC P16 connector configurable as one 8X or two 4X gigabit serial links to the FPGA

#### Memory

Option 150: Two 8 MB QDRII+ SRAM memory banks, 400 MHz DDR

Option 155 or 165: Two 512 MB DDR3

SDRAM memory banks, 400 MHz DDR

#### **PCI-Express Interface**

PCI Express Bus: Gen.1: x4 or x8; Gen 2: x4

#### Environmental

**Operating Temp:** 0° to 50° C **Storage Temp:** –20° to 90° C

**Relative Humidity:** 0 to 95%, non-cond. **Size:** Standard XMC module, 2.91 in. x 5.87 in.

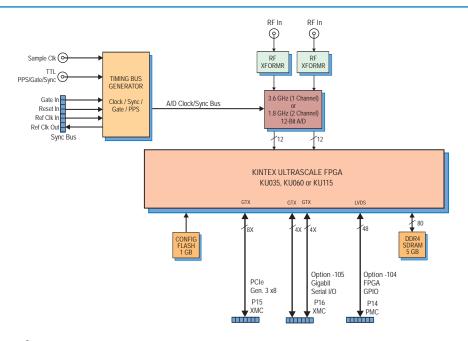

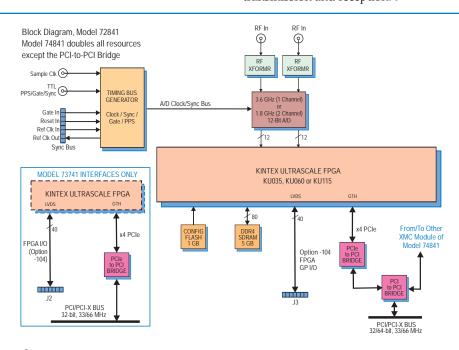

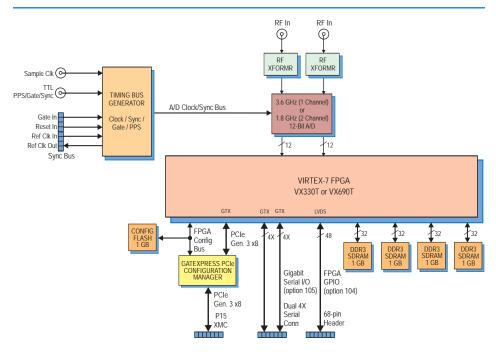

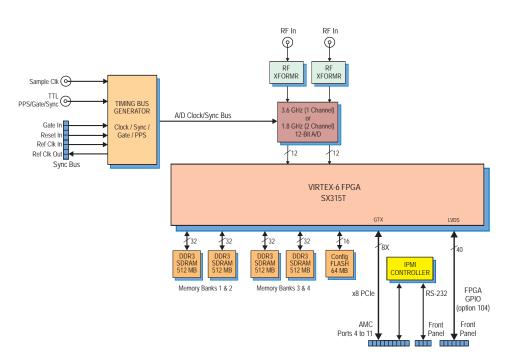

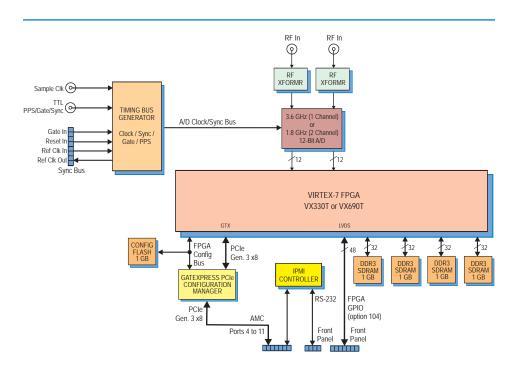

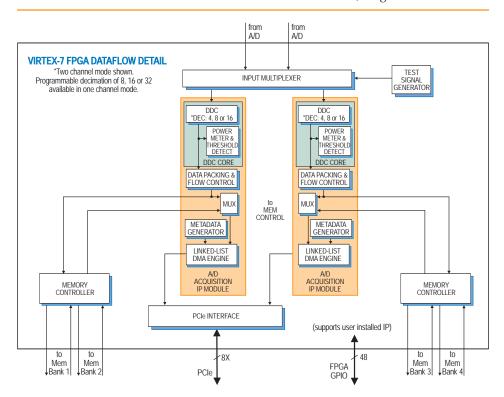

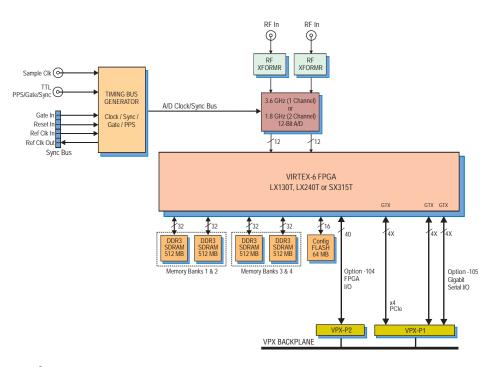

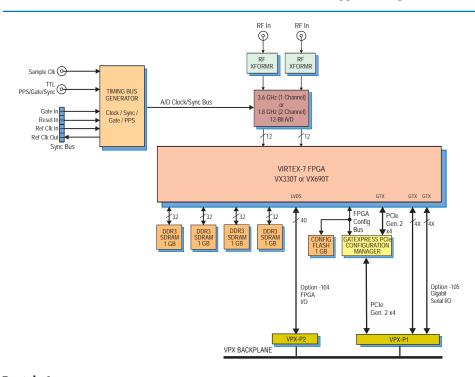

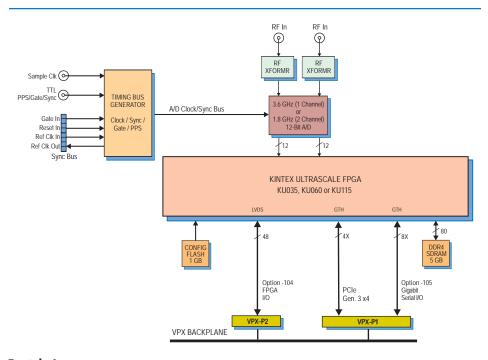

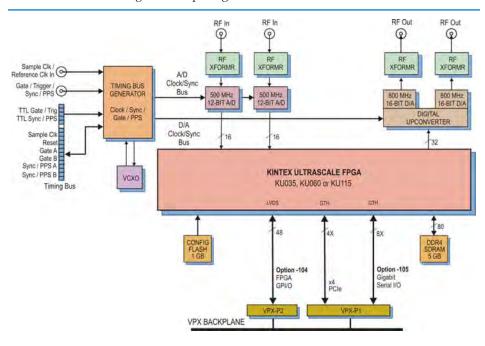

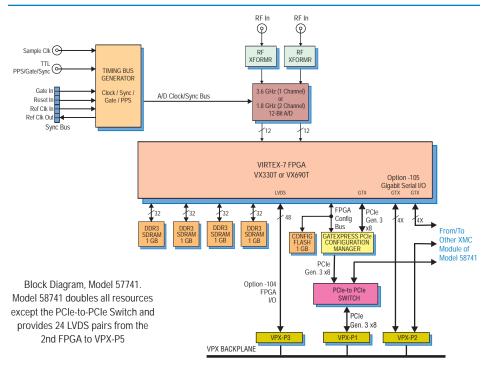

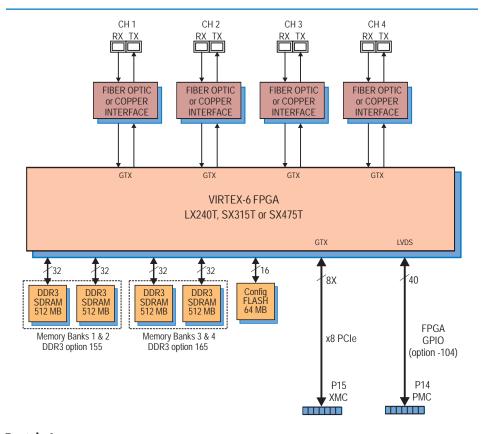

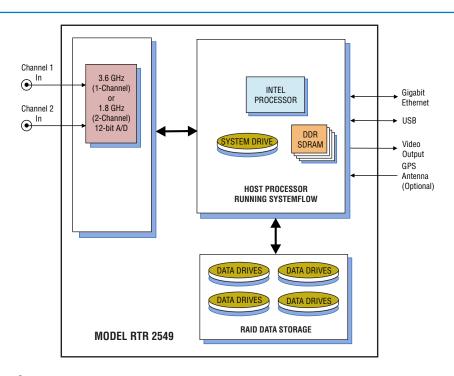

#### **Features**

- Ideal radar and software radio interface solution

- Supports Xilinx Virtex-6 LXT and SXT FPGAs

- One-channel mode with 3.6 GHz, 12-bit A/D

- Two-channel mode with 1.8 GHz, 12-bit A/Ds

- 2 GB of DDR3 SDRAM

- Sync bus for multimodule synchronization

- PCI Express Gen. 2 interface x8 wide

- Optional user-configurable gigabit serial interface

- Optional LVDS connections to the Virtex-6 FPGA for custom I/O

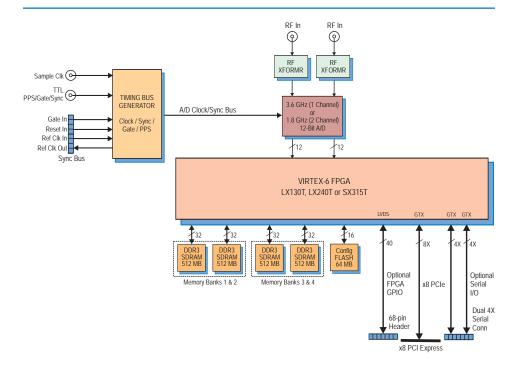

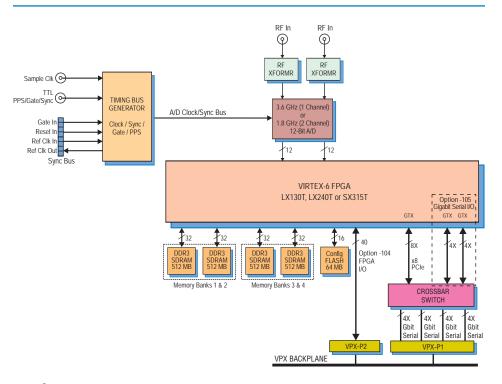

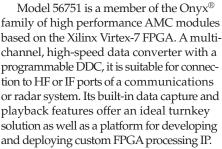

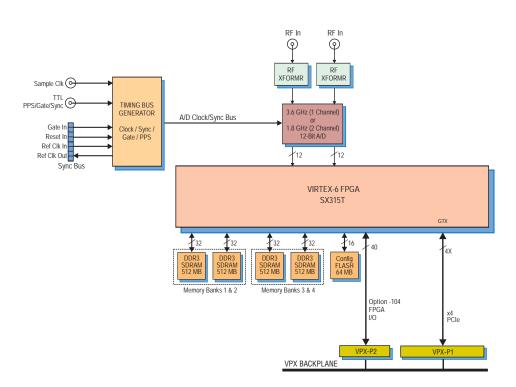

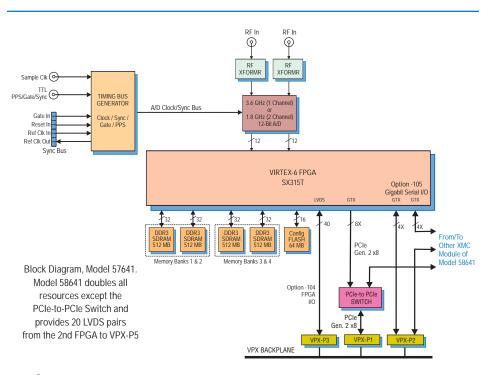

#### **General Information**

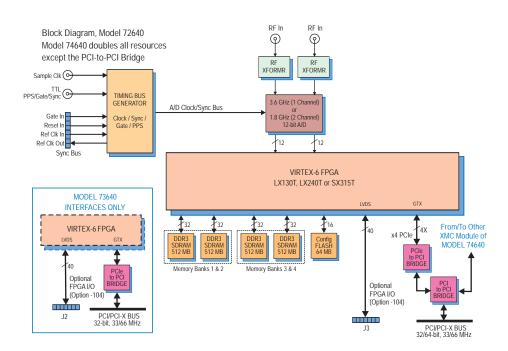

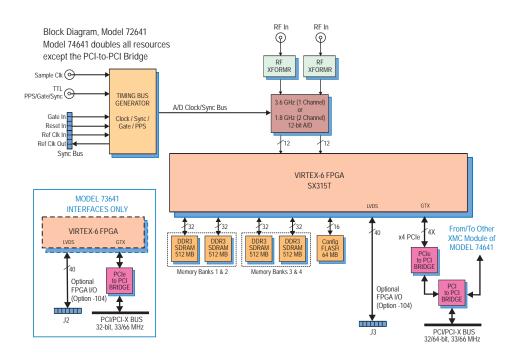

Model 71640 is a member of the Cobalt® family of high performance XMC modules based on the Xilinx Virtex-6 FPGA. A high-speed data converter, it is suitable for connection to HF or IF ports of a communications or radar system. Its built-in data capture features offer an ideal turnkey solution as well as a platform for developing and deploying custom FPGA processing IP.

It includes a 3.6 GHz, 12-bit A/D converter and four banks of memory. In addition to supporting PCI Express Gen. 2 as a native interface, the Model 71640 includes optional general purpose and gigabit serial connectors for application-specific I/O.

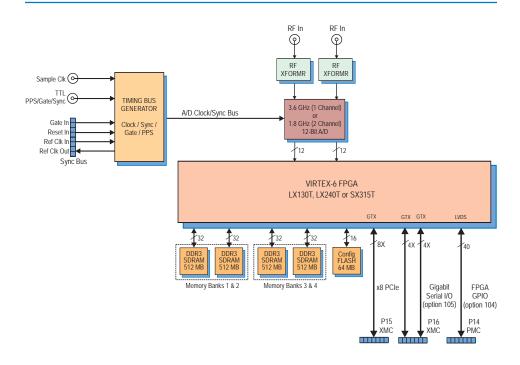

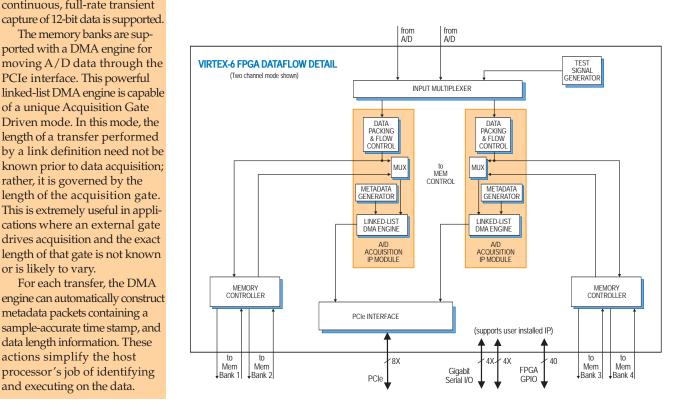

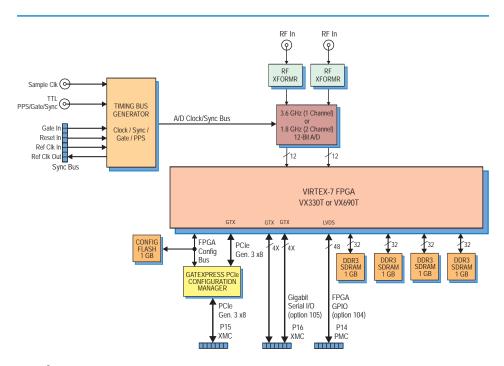

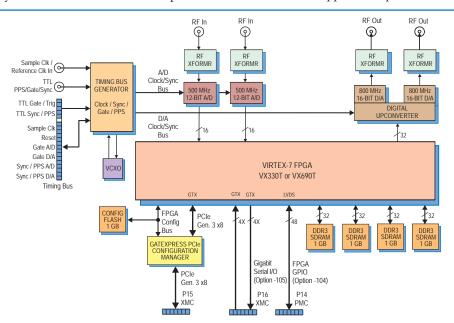

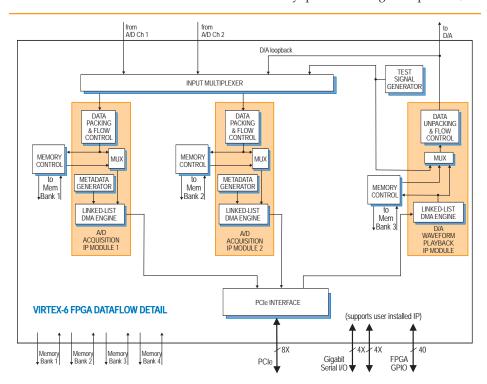

## **The Cobalt Architecture**

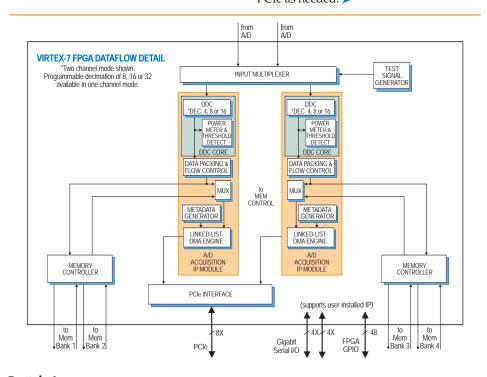

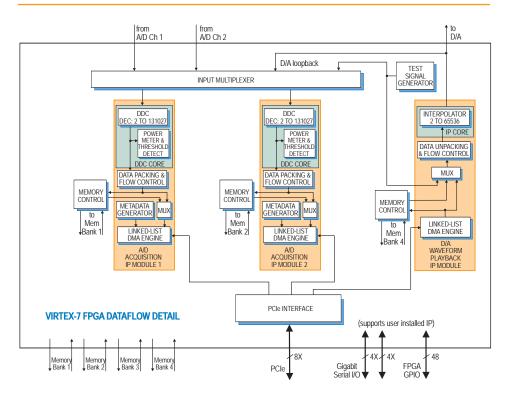

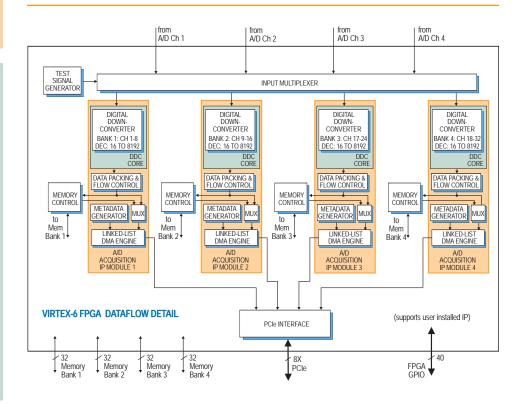

The Pentek Cobalt architecture features a Virtex-6 FPGA. All of the board's data and control paths are accessible by the FPGA, enabling factory-installed functions including data multiplexing, channel selection, data packing, gating, triggering and memory control. The Cobalt architecture organizes the FPGA as a container for data processing applications where each function exists as an intellectual property (IP) module.

Each member of the Cobalt family is delivered with factory-installed applications ideally matched to the board's analog interfaces. The 71640 factory-installed functions include an A/D acquisition IP module. In addition, IP modules for DDR3 memories, a controller for all data clocking and synchronization functions, a test signal generator

and a PCIe interface complete the factory-installed functions and enable the 71640 to operate as a complete turnkey solution, without the need to develop any FPGAIP.

## **Extendable IP Design**

For applications that require specialized functions, users can install their own custom IP for data processing. Pentek GateFlow® FPGA Design Kits include all of the factory installed modules as documented source code. Developers can integrate their own IP with the Pentek factory-installed functions or use the GateFlow Design Kit to completely replace the Pentek IP with their own.

## **Xilinx Virtex-6 FPGA**

The Virtex-6 FPGA site can be populated with a variety of different FPGAs to match the specific requirements of the processing task. Supported FPGAs include: LX130T, LX240T, or SX315T. The SXT part features 1344 DSP48E slices and is ideal for modulation/demodulation, encoding/decoding, encryption/decryption, and channelization of the signals between transmission and reception. For applications not requiring large DSP resources, one of the lower-cost LXT FPGAs can be installed.

Option -104 installs the P14 PMC connector with 20 pairs of LVDS connections to the FPGA for custom I/O.

Option -105 installs the P16 XMC connector with dual 4X gigabit links to the FPGA to support other serial protocols. >

# ➤ A/D Converter Stage

The front end accepts analog HF or IF inputs on a pair of front panel SSMC connectors with transformer coupling into a Texas Instruments ADC12D1800 12-bit A/D. The converter operates in single-channel interleaved mode with a sampling rate of 3.6 GHz and an input bandwidth of 1.75 GHz; or, in dual-channel mode with a sampling rate of 1.8 GHz and input bandwidth of 2.8 GHz.

The ADC12D1800 provides a programmable 15-bit gain adjustment allowing the 71640 to have a full scale input range of +2 dBm to +4 dBm. A built-in AutoSync feature supports A/D synchronization across multiple modules.

The A/D digital outputs are delivered into the Virtex-6 FPGA for signal processing, data capture or for routing to other module resources.

## **Clocking and Synchronization**

The 71640 accepts a 1.8 GHz dual-edge sample clock via a front panel SSMC connector. A second front panel SSMC accepts a TTL signal that can function as Gate, PPS or Sync.

A front panel multi-pin sync bus connector allows multiple modules to be synchronized, ideal for larger multichanel systems. The sync bus includes gate, reset and in and out reference clock signals. Multiple 71640s can be synchronized using the Cobalt high speed sync module to drive the sync bus.

### **Memory Resources**

The 71640 architecture supports four independent memory banks of DDR3 SDRAM. Each bank is 512 MB deep and is an integral part of the module's DMA and data capture capabilities. Built-in memory functions include an A/D data transient capture mode for taking snapshots of data for transfer to a host computer.

In addition to the factory-installed functions, custom user-installed IP within the FPGA can take advantage of the memories for many other purposes.

#### **XMC Interface**

The Model 71640 complies with the VITA 42.0 XMC specification. Two connectors each provide dual 4X links or a single 8X link with up to a 5 GHz bit clock. With dual XMC connectors, the 71640 supports x8 PCIe on the first XMC connector leaving the optional second connector free to support user-installed transfer protocols specific to the target application.

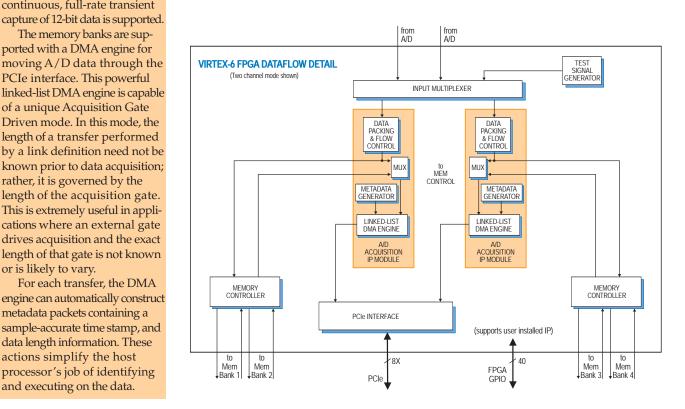

## module can receive data from the A/D, or a test signal generator. The IP module has associated memory banks for buffering data in FIFO mode or for storing data in transient capture mode. In single-channel mode, all four

A/D Acquisition IP Module

The 71640 features an A/D

Acquisition IP Module for easy

capture and data moving. The IP

banks are used to store the single-channel of input data. In dual-channel mode, memory banks 1 and 2 store data from input channel 1 and memory banks 3 and 4 store data from input channel 2. In both modes,

continuous, full-rate transient

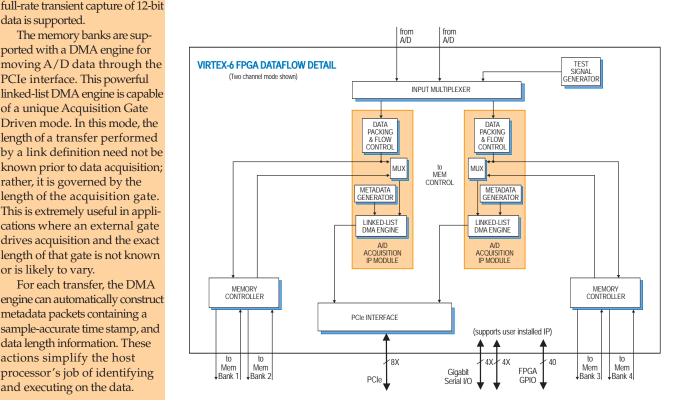

The memory banks are supported with a DMA engine for moving A/D data through the PCIe interface. This powerful linked-list DMA engine is capable of a unique Acquisition Gate Driven mode. In this mode, the length of a transfer performed by a link definition need not be known prior to data acquisition; rather, it is governed by the length of the acquisition gate. This is extremely useful in applications where an external gate drives acquisition and the exact length of that gate is not known or is likely to vary.

For each transfer, the DMA engine can automatically construct metadata packets containing a sample-accurate time stamp, and data length information. These actions simplify the host processor's job of identifying and executing on the data.

## **Model 8266**

The Model 8266 is a fully-integrated PC development system for Pentek Cobalt, Onyx and Flexor PCI Express boards. It was created to save engineers and system integrators the time and expense associated with building and testing a development system that ensures optimum performance of Pentek boards.

## **➤ PCI Express Interface**

The Model 71640 includes an industry-standard interface fully compliant with PCI Express Gen. 1 & 2 bus specifications. The x8 lane interface includes multiple DMA controllers for efficient transfers to and from the module.

## **Specifications**

#### Front Panel Analog Signal Inputs

**Input Type:** Transformer-coupled, front panel female SSMC connectors

#### A/D Converter

**Type:** Texas Instruments ADC12D1800 **Sampling Rate:** Single-channel mode: 500 MHz to 3.6 GHz; dual-channel mode: 150 MHz to 1.8 GHz

Resolution: 12 bits

Input Bandwidth: single-channel mode: 1.75 GHz; dual-channel mode: 2.8 GHz Full Scale Input: +2 dBm to +4 dBm, programmable

Sample Clock Sources: Front panel SSMC connector

**Sync Bus:** Multi-pin connectors, bus includes gate, reset and in and out ref clock

#### **External Trigger Input**

**Type:** Front panel female SSMC connector, TTL

**Function:** Programmable functions include: trigger, gate, sync and PPS

#### Field Programmable Gate Array

Standard: Xilinx Virtex-6 XC6VLX130T-2 Optional: Xilinx Virtex-6 XC6VLX240T-2, or XC6VSX315T-2

#### Custom I/O

**Option -104:** Installs the PMC P14 connector with 20 LVDS pairs to the FPGA

**Option -105:** Installs the XMC P16 connector configurable as one 8X or two 4X gigabit serial links to the FPGA

**Memory:** Four 512 MB DDR3 SDRAM memory banks, 400 MHz DDR

#### **PCI-Express Interface**

**PCI Express Bus:** Gen. 1 or Gen. 2: x4 or x8

#### **Environmental**

Operating Temp: 0° to 50° C Storage Temp: -20° to 90° C Relative Humidity: 0 to 95%, non-cond. Size: Standard XMC module, 2.91 in. x 5.87 in.

## **Ordering Information**

| Model | Description            |

|-------|------------------------|

| 71640 | 1-Ch. 3.6 GHz or 2-Ch. |

|       | 1.8 GHz, 12-bit A/D,   |

|       | Virtex-6 FPGA - XMC    |

#### Ontions

| Options. |                                                          |

|----------|----------------------------------------------------------|

| -002*    | -2 FPGA speed grade                                      |

| -062     | XC6VLX240T                                               |

| -064     | XC6VSX315T                                               |

| -104     | LVDS FPGA I/O through P14 connector                      |

| -105     | Gigabit serial FPGA I/O through P16 connector            |

| -155*    | Two 512 MB DDR3<br>SDRAM Memory Banks<br>(Banks 1 and 2) |

| -165*    | Two 512 MB DDR3<br>SDRAM Memory Banks<br>(Banks 3 and 4) |

<sup>\*</sup> These options are always required

Contact Pentek for availability of rugged and conduction-cooled versions

Model Description

8266 PC Development System See 8266 Datasheet for

Options

# 1-Ch. 3.6 GHz or 2-Ch. 1.8 GHz, 12-bit A/D, w/ Wideband DDC, Virtex-6 FPGA - XMC

#### **Features**

- Ideal radar and software radio interface solution

- One-channel mode with 3.6 GHz, 12-bit A/D

- Two-channel mode with 1.8 GHz, 12-bit A/Ds

- Programmable one- or twochannel DDC (Digital Downconverter)

- 2 GB of DDR3 SDRAM

- Sync bus for multimodule synchronization

- PCI Express Gen. 2 interface up to x8

- Optional LVDS connections to the Virtex-6 FPGA for custom I/O

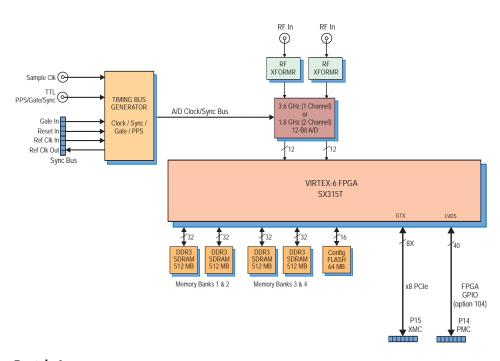

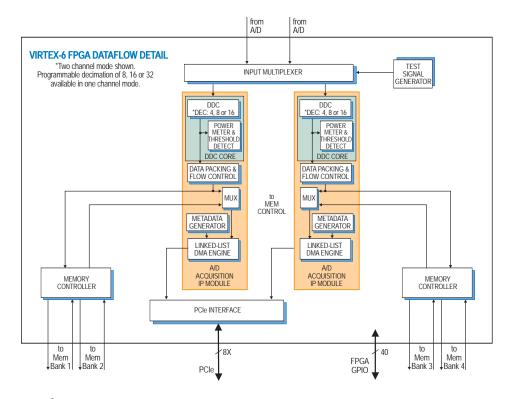

### **General Information**

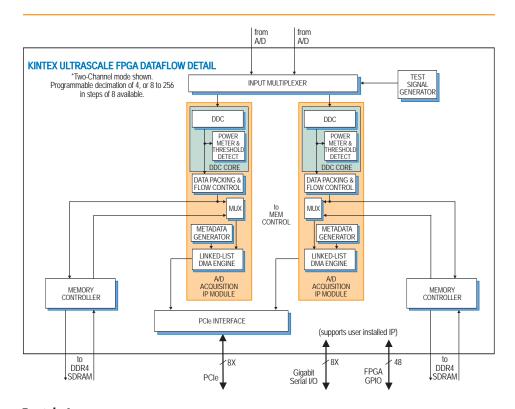

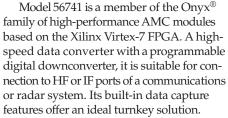

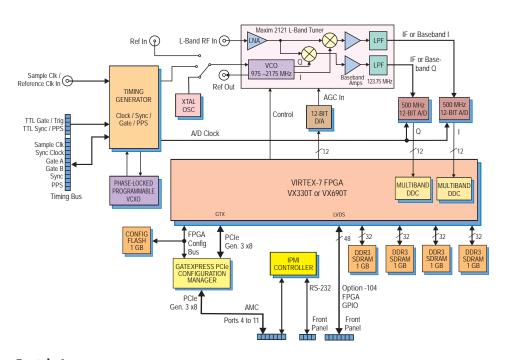

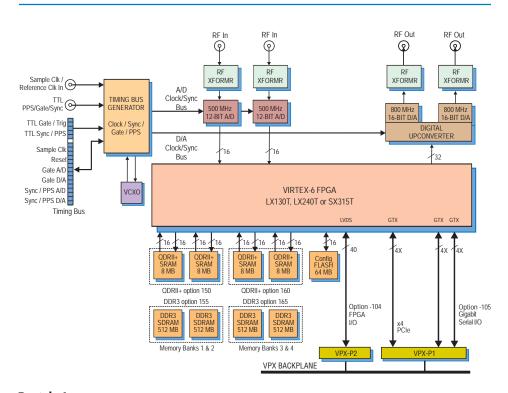

Model 71641 is a member of the Cobalt® family of high-performance XMC modules based on the Xilinx Virtex-6 FPGA. A high-speed data converter with a programmable digital downconverter, it is suitable for connection to HF or IF ports of a communications or radar system. Its built-in data capture features offer an ideal turnkey solution.

It includes a 3.6 GHz, 12-bit A/D converter and four banks of memory. In addition to supporting PCI Express Gen. 2 as a native interface, Model 71641 includes an optional connection to the Virtex-6 FPGA for custom I/O .

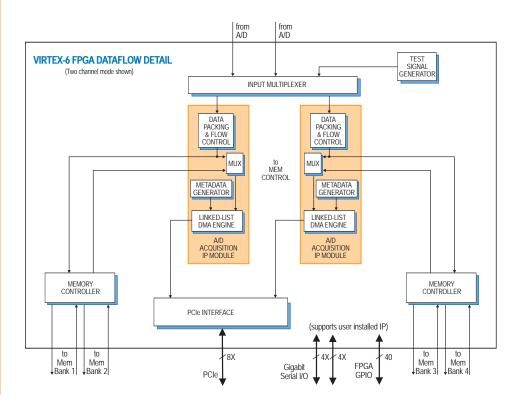

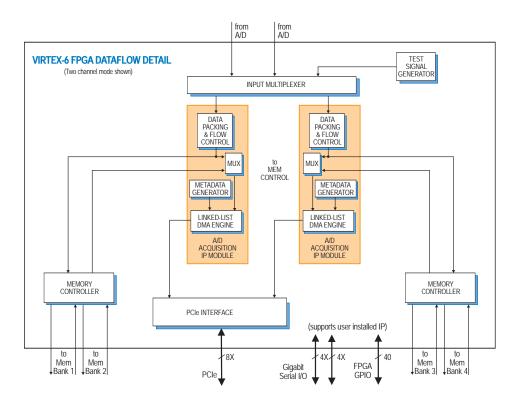

#### **The Cobalt Architecture**

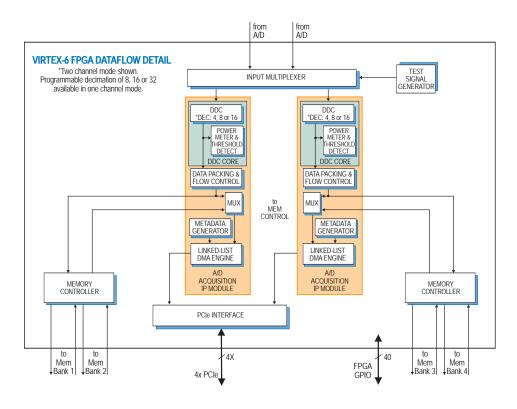

The Pentek Cobalt architecture features a Virtex-6 FPGA. All of the board's data and control paths are accessible by the FPGA, enabling factory-installed functions including data multiplexing, channel selection, data packing, gating, triggering and memory control. The Cobalt architecture organizes the FPGA as a container for data processing applications where each function exists as an intellectual property (IP) module.

Each member of the Cobalt family is delivered with factory-installed applications ideally matched to the board's analog interfaces. The 71641 factory-installed functions include an A/D acquisition IP module. In addition, IP modules for DDR3 memories, a

controller for all data clocking and synchronization functions, a test signal generator and a PCIe interface complete the factory-installed functions and enable the 71641 to operate as a complete turnkey solution, without the need to develop any FPGA IP.

For applications that require additional control and status signals, option -104 installs the P14 PMC connector with 20 pairs of LVDS connections to the FPGA for custom I/O.

## A/D Converter Stage

The front end accepts analog HF or IF inputs on a pair of front panel SSMC connectors with transformer coupling into a Texas Instruments ADC12D1800 12-bit A/D. The converter operates in single-channel interleaved mode with a sampling rate of 3.6 GHz and an input bandwidth of 1.75 GHz; or, in dual-channel mode with a sampling rate of 1.8 GHz and input bandwidth of 2.8 GHz.

The ADC12D1800 provides a programmable 15-bit gain adjustment allowing the 71641 to have a full scale input range of +2 dBm to +4 dBm. A built-in AutoSync feature supports A/D synchronization across multiple modules.

The A/D digital outputs are delivered into the Virtex-6 FPGA for signal processing, data capture or for routing to other module resources.

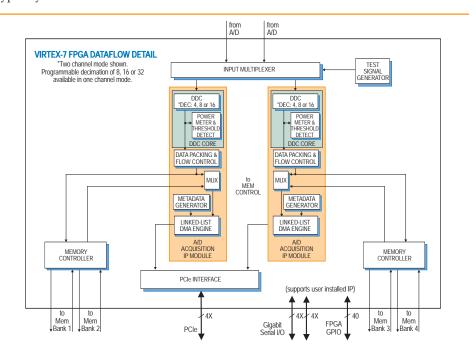

# 1-Ch. 3.6 GHz or 2-Ch. 1.8 GHz, 12-bit A/D, w/ Wideband DDC, Virtex-6 FPGA - XMC

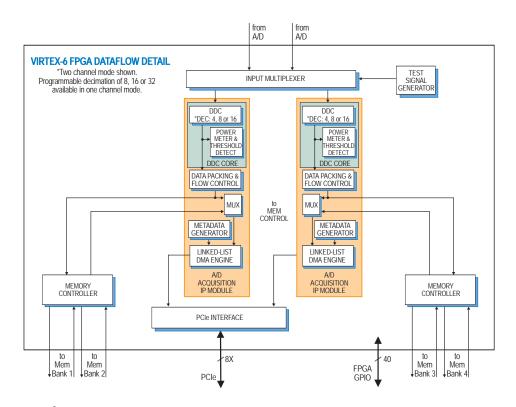

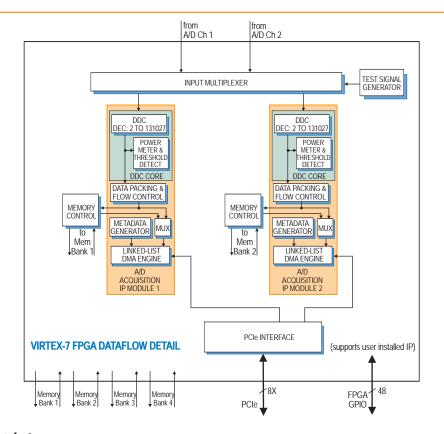

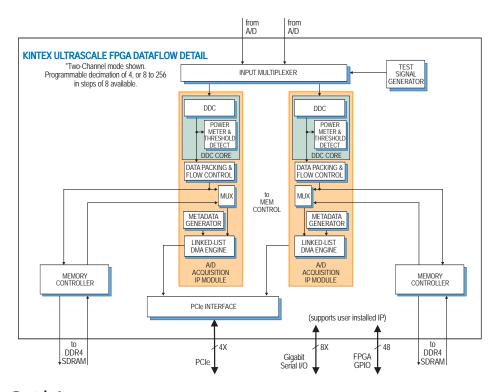

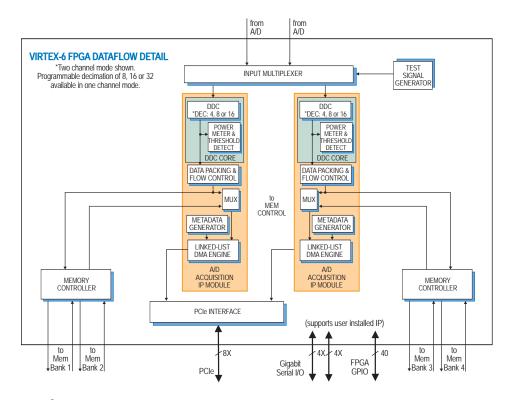

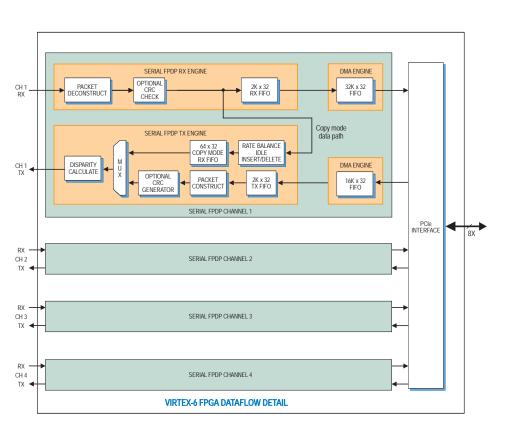

## A/D Acquisition IP Module

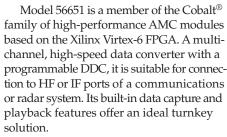

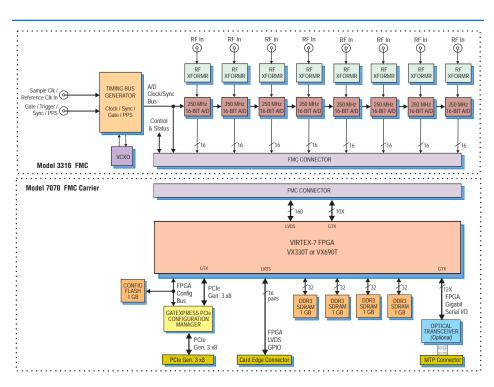

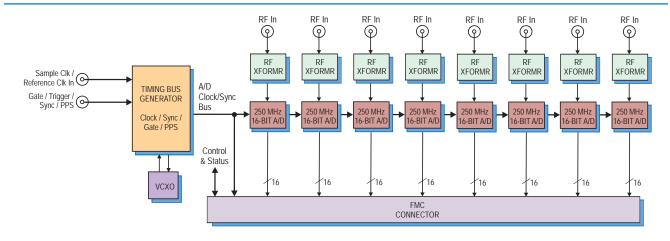

The 71641 features an A/D Acquisition IP Module for easy capture and data moving. The IP module can receive data from the A/D, or a test signal generator. The IP module has associated memory banks for buffering data in FIFO mode or for storing data in transient capture mode. In single-channel mode, all four banks are used to store the single-channel of input data. In dual-channel mode, memory banks 1 and 2 store data from input channel 1 and memory banks 3 and 4 store data from input channel 2. In both modes, continuous, full-rate transient capture of 12-bit data is supported.