Pentek, Inc. http://www.pentek.com ine arterly publication for engineering system design and applications.

#### Fall 1999 • Vol. 8, No. 3

One Park Way, Upper Saddle River, NJ 07458 Tel: (201) 818-5900 • Fax: (201) 818-5904 email: pipeline@pentek.com

© 1999 Pentek, Inc. Newsletter Editor: TNT Resources

# Pentek Helps JPL Improve the Deep Space Network

anaged and operated for NASA by the Jet Propulsion Laboratory (JPL), the Deep Space Network (DSN) is an international network of antennas. It supports interplanetary spacecraft missions and radio astronomy observations for the exploration of the solar system and the universe. The network also supports selected Earth-orbiting missions.

Presently, the DSN consists of three deep-space communications facilities strategically placed approximately 120 degrees apart around the world. These facilities are located at Goldstone, in California's Mojave Desert, near Madrid, Spain and near Canberra, Australia. The placement permits continuous observation of spacecraft as the Earth rotates, and helps to make the DSN the largest and most sensitive communications system in the world.

NASA's scientific investigation of the solar system is being accomplished mainly through the use of unmanned spacecraft. The DSN provides a vital two-way communications link that guides and controls these planetary explorers, and brings back the image and new data they collect.

#### The DSN Antennas

Each DSN site employs at least four deep space stations equipped with steerable high-gain, parabolic reflector antennas. They include:

- Two 34-meter diameter antennas

- One 26-meter antenna

- One 70-meter antenna

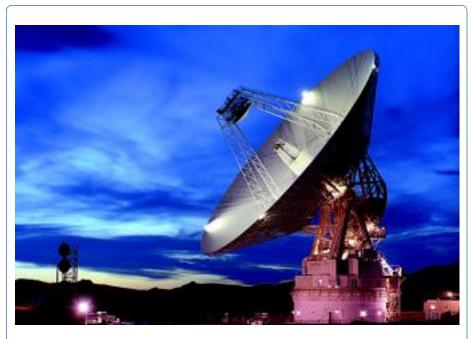

The 70-meter antenna at Goldstone, California is shown in Figure 1. To appreciate its size, you might want to refer to the length of a football stadium of 100 yards, or 300 feet. This antenna is 230 feet in diameter, or roughly 34 the length of a football field!

Figure 1. The 70-m Antenna at Goldstone, CA (Courtesy of JPL)

Among others, the antennas and data delivery systems make it possible to:

- Acquire telemetry data from the spacecraft

- Transmit commands to it

- Track spacecraft position and velocity

- Perform scientific measurements and gather scientific data

- Monitor and control the performance of the network

#### **Getting the Picture**

Getting the picture is one of the tasks of the DSN. The digital data bit stream can be transmitted from a spacecraft at various frequencies. For instance, Galileo transmits in S-Band at rates up to 160 bits per second. At this rate, one 800 x 800 pixel image compressed 10:1, is received on Earth every 53 minutes. The data is received by any one of the three DSN sites around the world and then sent to JPL.

#### **Ranging System Update**

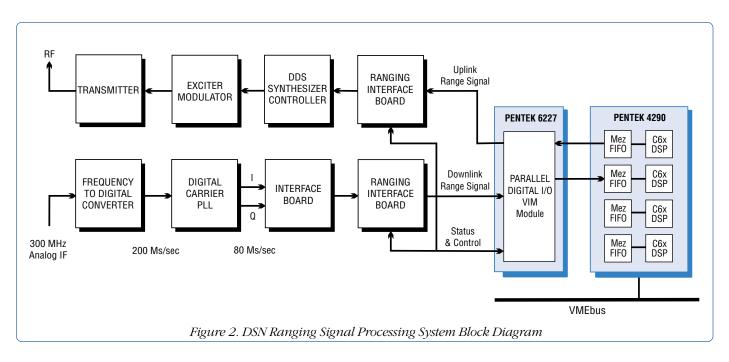

As part of JPL's Network Simplification Program, the existing spacecraft ranging system has been updated using a smaller hardware design that is easier to operate and maintain. Three VME boards have replaced a full rack of tracking and ranging equipment. The Pentek Model 4290 Quad 'C6x DSP processor board handles the main processing, while the Model 6227 Parallel Digital I/O VIM module provides the interface to the 4290 synchronous BI-FIFOs for 16-bit parallel data in and out at rates up to 100 Mbytes/sec.

"The old DSN ranging design used custom-made boards to correlate the received ranging signal against the expected pattern and accumulate the correlation result in hardware," said Scott Bryant, telecommunications engineer, JPL. "Faster DSP technology has [Continued on page 2]

# Pentek Helps JPL Improve the Deep Space Network

#### [Continued from page 1]

enabled a new DSN ranging design that can handle the digital ranging signal directly through use of FIFOs. The new design reduces hardware count by eliminating custom correlator VME boards. It also eliminates several interface boards and related hardware. The use of COTS DSP boards reduces the cost and development time of the spacecraft ranging effort," he added.

### **Signal Processing**

As shown in Figure 2, the downlink 300 MHz IF is applied to a frequencyto-digital converter, which, in turn, outputs a 200 Ms/sec digitized version of the IF signal. This signal is then applied to a digital phase-lock-loop which provides in-phase and quadrature (I and Q) components of the downlink signal at 80 Ms/sec. Two interface boards are used to route these signals to the Model 4290 with a 6227 Parallel Digital I/O VIM module. These are used to produce a ranging modulation at up to 4 MHz frequency, sample the received digital ranging signal at up to 16 MHz, and buffer the input in the BI-FIFOs of the 4290. The 4290 then integrates the received ranging signal

inside the processor application code and correlates the ranging signal against any software-configurable ranging tone to produce the range phase measurement.

The uplink signal is generated by the 4290 and is routed through the 6227 to an interface board. The signal is then applied to a direct digital synthesizer controller and is upconverted to the uplink carrier frequency. This signal then drives the transmitter exciter modulator, thereby completing the ranging control system.

The Model 4290 provides the processor and FIFO input/output speed required for the new DSN spacecraft ranging design. The Model 6227 provides simple input/output and control connections to the DSN receiver hardware. The 4290 memory design, processor speed, and development tools allow for developing the entire ranging application in C language without having to resort to assembly code.

The Model 6227 features two highspeed parallel data ports plus a third control/status port. The two streaming data ports are 16-bit parallel data busses using single-ended TTL lines, one serving as the input and the other as " The new design reduces hardware count by eliminating custom correlator VME boards. It also eliminates several interface boards and related hardware. The use of COTS DSP boards reduces the cost and development time of the spacecraft ranging effort. "

Scott Bryant, JPL Telecommunications

the output. The bidirectional 16-bit control/status port is suitable for monitoring and controlling specific functions on peripheral devices.

#### **About VIM Modules**

Besides the 6227, Pentek's newly introduced VIM module family includes A/D converters, narrowband and wideband digital receivers with integral A/Ds and demodulators, front panel data port (FPDP) and 'C40 comm port interfaces, and digital upconverters with D/As. For more information on these and other Pentek products, visit our website at **www.pentek.com.**

# Pentek ReadyFlow<sup>™</sup> - Board Support Libraries

*[Continued from page 4]* will also help you get an immediate start on writing your own application without having to reinvent the wheel. They provide sample code that is known to work, giving you, the new user, a means of verifying that your board set is operational.

Separate source and header files are included for each board-level product made by Pentek. The source files generally allow you to select either polling or interrupts as the means of determining when the device requires service.

#### Example, Model 4290 Processor

As an example of a processor board, the Model 4290 library includes:

- Header files

- Cache, DMA, EMIF, interrupts, serial ports, timer

- General DSP board functions

- Reading and writing to mezzanine FIFOs

- Reading and writing to interprocessor FIFOs

- Programming DMA reads and writes

- Programming interrupts

- Using the mailboxes

- Sending interprocessor semaphores

- Managing dual-port and global memory resources

#### Example, Model 6210 VIM

As an example of a VIM module, the Model 6210 Digital Receiver includes the following:

- Definition of 6210 data structures

Control registers, digital

- receiver and board parameters

- Parameter definitions

- Function, range and notation of parameters used

- □ High-level functions

- Initialize control registers and receivers to parameters stored in tables with a single function call

- □ Intermediate-level functions

- Groups of control functions for each section of the board

- Called by high-level functions or directly

- Low-level functions and macros

- Called by intermediate-level functions or directly

- Control of individual registers

- Minimize software overhead when only a few parameters are changed

- Optimize execution speed

## Pentek SwiftNet™ Release 3.5 Offers Effortless Upgrade

Release 3.5, the newest version of SwiftNet networking and communication software operates in a true Windows 95/98/NT environment with the graphical user interface appearing as one icon on the tool bar.

Other new features include SwiftNet Autostart which eliminates the need to manually invoke the program, control windows for DSP-to-host nodes that automatically save system configuration files, and an improvement of J-TAG performance by a factor of two to three.

New products supported in Release 3.5 include, among others, drivers for the SBS Technologies, Inc. Pentiumbased embedded connectivity products.

Pentek's flagship software product, SwiftNet is a powerful networking protocol that links your workstation and software development tools to your VMEbus DSP processors. SwiftNet treats DSP processors as network devices and supports a wide range of platforms, tools and boards, thereby improving the development environment.

SwiftNet is based on an applications programming interface (API). The

SwiftNet API is a collection of C-language library functions that allows users to write a custom application using the SwiftNet protocol. It gives you the interoperability that is needed in multiplatform systems.

SwiftNet is the ultimate host-totarget link for DSP code development because it adapts easily to any sys-

tem configuration from simple singleprocessor boards to extensive multiprocessor systems in remote locations. Since it is based on the TCP/IP protocol, it even makes DSP development over the Internet or Intranets practical. Workgroups with several workstations linked by Ethernet can also use SwiftNet to access the same VMEbus card cage.

|                                     | Manual Institutes                | TO WARD                                         | 10                             |

|-------------------------------------|----------------------------------|-------------------------------------------------|--------------------------------|

|                                     | Portras Pouring<br>Posts Pouring | Acces<br>STEVE-AC<br>LINA<br>D-RER-PC<br>ZTANDA | 3.5.2<br>3.2 fets<br>3.4 signs |

| Tengits   Menory   Hole Information |                                  |                                                 |                                |

| time .                              | fram<br>Rode 4204 HEF task board | Add Vodete                                      | Delete                         |

|                                     |                                  | Picperties 1                                    |                                |

|                                     |                                  |                                                 |                                |

| ANTER Parame                        | net Inst Sea                     |                                                 |                                |

| 17 Loui ordpath                     |                                  | Swif                                            | tNe                            |

|                                     |                                  |                                                 | Version 3                      |

|                                     | Earol Help                       |                                                 |                                |

SwiftNet one-time configuration setup for the Model 4284 'C40 DSP Baseboard

> SwiftNet even allows each developer to access different DSP chips on the same multiprocessor board. Basically, you can share your data with as many users as needed wherever they are located.

For upgrades or more information on SwiftNet, call Pentek Sales at 201-818-5900.

*<b>Sumple Signature* **Series**

| Þ | Pentek ReadyFlow   |

|---|--------------------|

| £ | SwiftNet, Ver. 3.5 |

| Į | The JPL DSN Networ |

### at DSPWorld sU fisiV

**Booths 301 & 302** November 3-4, 1999 Orlando, Florida Orange County Convention Center

Come see the latest in 'C6x products

somab avil bns

- cations

- Initialization and test Data movement and communi-

- ۲

- programs C-callable functions

- Build object libraries • Compile and link application

- □ A "How to" section

These libraries:

completion

the board-level product, such as:

In general, functions appropriate to

### What's Included in the Libraries

- Include complete source code for all functions

- □ Are illustrated with many examples

Provide development tools for

□ Allow programming at high,

- meet various needs

quick start-up through application

- intermediate and low levels to

The examples included provide the

occur with first-time users of Pentek

answers to most of the questions that

products. These programming examples

Backplane I/O

- Control of board resources

- Header files for board-specific parameters

- Mezzanine peripheral I/O

PERMIT No. 625 Uewark, NJ PAID **JOATZOG .2.U 1ST CLASS MAIL PRESORT**

with the hardware itself. To address this issue, Pentek has developed ReadyFlow Board Support Libraries for all its board-level products.

New Development Tools for Quick Start-Up and Application Completion

mentation often find themselves

frustrated by the fact that when their

able to put them to immediate use.

Because these instruments are largely

software controlled, a certain amount

in order to put the new cards through

their paces. Then, if something does

not go as planned, there is no way to

with the new code you've written, or

know for sure whether the problem lies

of programming is generally necessary

new devices are delivered, they are un-

New users of card-cage based instru-

[Continued on page 3]