## NRL Designs a COTS Radar Data Collection and Analysis System

ast year, as part of its ongoing research effort, scientists in the Radar Division of the Naval Research Laboratory, Washington, DC decided to develop a radar data collection and analysis system for quick hook-up to a ship's radar. The system had to meet the following prime objectives:

• **COTS.** The system was to be comprised entirely of commercial off-the-shelf products.

• **Portability.** The system was to be portable, so that it could easily travel aboard scheduled air carriers and taken from ship to ship.

• **Flexibility.** The system had to be compatible with both, analog and digital radars and accommodate both, online, and post processing and signal analysis.

• Upgradeability. To allow for modularity and future updates as new and improved components become available, the system had to be VMEbusbased.

Computer I/O Corporation, Laurel MD was selected to provide this system. Computer I/O specializes in delivering turnkey systems that solve problems associated with getting data in and out of computers. The solutions to these problems are based upon the company's expertise in designing high-speed data acquisition and digital signal processing systems for radar and telecommunications applications.

Computer I/O came to Pentek for much of the VMEbus data acquisition and DSP hardware. Except for a special cable, everything from Pentek was COTS with fairly short deliveries.

#### System Overview

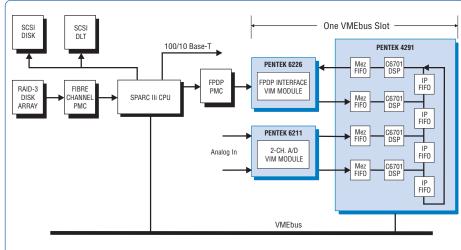

The radar data collection system shown in Figure 1 is used to capture, store, archive, and analyze wideband

Figure 1. The Radar Data Collection & Analysis System (Courtesy of Computer I/O)

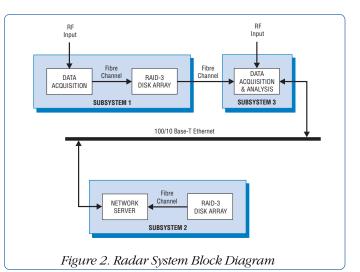

radar data. As shown in Figure 2, it provides the desired functionality using three separate hardware subsystems. The subsystems are comprised entirely of COTS products in 6U VME format. Subsystem 1 and Subsystem 3 are the field data acquisition and analysis units

and are mounted in portable VME enclosures. They are compact enough to be checked as standard luggage on commercial air carriers. Subsystem 2 is rack-mounted and is used only in the laboratory.

**Subsystem 1** consists of a configurable data acquisition system capable of synchronously digitizing two channels at rates up to 65 MHz and storing the data to a RAID-3 disk array via a Fibre Channel interface.

**Subsystem 2** supplies a Fibre Channel interface to a RAID-3 disk array and allows data retrieval from the RAID >>

## **NRL Designs a COTS Radar Data Collection and Analysis System**

for storage on a local SCSI disk or digital linear tape (DLT) drive. The subsystem also acts as a networkable file server allowing client computers to view the directory structure and retrieve data from the RAID.

**Subsystem 3** supplies data retrieval capabilities for analyzing data from the RAID by a DSP board and also acts as a networkable file server. The file server function allows users at client computers to retrieve data. The subsystem also provides for real-time data analysis capability through an alternate A/D converter with a direct path to the DSP board.

#### Signal Processing, Subsystem 1

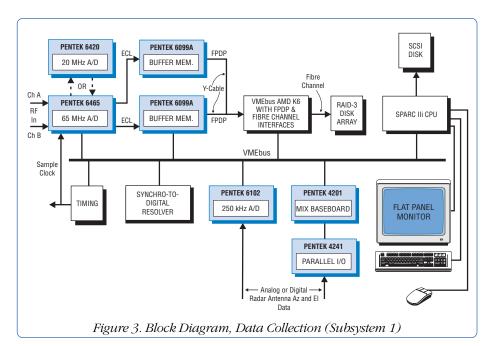

Shown in Figure 3, Subsystem 1 is a configurable data acquisition system housed in a portable 12-slot VME cage. Incoming RF radar signals are digitized by either a Pentek 6465 2-channel 12-bit 65 MHz A/D converter, or a Pentek 6420 2-channel 14-bit 20 MHz A/D converter. The user selects which converter to use, based on the requirements of the particular data collection run. In either case, the sampling clock is externally applied at the appropriate sampling frequency.

The digitized outputs are applied to two Pentek 6099A 512 MB buffers. Together, these buffers collect 1024 MB of data at the rate of 260 MB/sec. They also provide a transition from the ECL interface of the A/Ds to the front panel data port (FPDP) interface required by

the VMEbus AMD K6 board. The special "Y-cable" from Pentek allows for the contents of the two Model 6099A buffers to be combined and sent to the FPDP interface. The VMEbus AMD K6 CPU runs the highperformance Easy I/O<sup>™</sup> File System driver software and

stores the data to the RAID-3 disk array which has 72 GB storage capability. The File System has the ability to access disks at 50 MB/sec.

A COTS Synchro-to-Digital VMEbus converter is included. Its purpose is to provide additional data regarding ship roll compensation, when the data collection system is operated aboard a ship.

A Pentek 6102 A/D converter (configured with six channels) digitizes radar azimuth and elevation data with 16-bit resolution A/D converters, when the radar system is analog. When used with digital radar systems, one or two Pentek 4241 Parallel Digital I/O inter-

Figure 4. Block Diagram, File Server (Subsystem 2)

faces mounted on the Pentek 4201 MIX to VME Baseboard handle the azimuth and elevation data. One 4241 handles 32-bit data, while two 4241's handle 64-bit data.

A SPARC IIi VMEbus 300 MHz singleboard CPU utilizing Solaris 2.7 provides all system control and setup functions through the Easy I/O Data Flow application software. For user interaction with the subsystem, a standard keyboard, mouse, a flat panel monitor, and a SCSI disk are included.

### Signal Processing, Subsystem 2

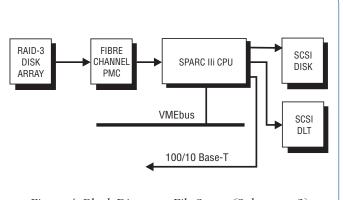

Shown in Figure 4, Subsystem 2 supplies a Fibre Channel interface to a RAID-3 disk array and allows data to be retrieved and stored on a local SCSI disk or SCSI digital linear tape (DLT). Subsystem 2 also serves as a file server for local clients to retrieve data via the 100 Base-T local area network. This subsystem does not have input device or display graphics capability, since it is not intended for operation as a standalone computer workstation.

Again, a SPARC IIi CPU equipped with a Fibre Channel PMC card is used as a slot 1 controller, running Solaris 2.7 and the Easy I/O Data Retrieval and Archiving server applications. >>

# Quad 'C6203 from Pentek reaches up to 9600 MIPS

#### [From page 4]

through the 'C6203's Expansion Bus, one for mezzanine I/O and two for interprocessor communication. Each BI-FIFO is organized as a pair of 1k x 32 FIFOs, one FIFO for each direction.

The mezzanine BI-FIFO connects data-streaming devices located on the mezzanine boards to the Expansion Bus (XB) of the 'C6203 and supports data transfers up to 300 MB/sec. The BI-FIFO effectively decouples the mezzanine device data flow and allows the 'C6203 to efficiently move data blocks in both directions for maximum processor utilization.

The interprocessor BI-FIFOs connect the Expansion Bus of adjacent 'C6203's and are ideal for pipelined processing applications. Block transfers, in both directions, at rates up to 300 MB/sec minimize data movement overhead and maximize interprocessor communications speed.

A private bus I/O BI-FIFO is used by each processor to transfer blocks of data to global resources such as the VMEbus, global SRAM, the PMC site, and the optional RACE++ interface. These BI-FIFOs are very effective in decoupling the 'C6203's from these resources and eliminating wait cycles while allowing 300 MB/sec block transfers.

#### **Global Bus Resources**

The global bus is supported by 16 MB of fast SDRAM accessible by all processors, the VMEbus, the PMC site, and the RACE++ interface. It is also supported by 1 MB flash EEPROM for factory-supplied firmware for global resource initialization and self test, and user-set board configuration parameters.

#### **VME64** Interface

All four processors can master the VMEbus using the industry standard Universe IIB VME64 interface chip. As a VMEbus slave, Model 4292 presents the global SDRAM, the four Bus I/O BI-FIFOs, and the PMC site as memory mapped resources.

### **Optional RACE++ Interface**

Delivering up to 267 MB/sec data transfers between VME boards, the optional RACE++ interface occupies the PMC connector and allows all four processors to send and receive RACEway packets using the Bus I/O BI-FIFOs as private data buffers.

For more information on the Model 4292 visit our website at: http://www.pentek.com

Figure 5. Block Diagram, Data Analysis (Subsystem 3)

direct path to the processor for real-time data analysis capability, and completes the Pentek "one-slot solution".

#### **Project Update**

The system is currently undergoing acceptance testing at Computer I/O and should be at NRL by the time this Pipe-line issue is printed.

"The performance and integration effort expended by Pentek and Computer I/O met NRL's requirements," said Kim Scheff, Scientist, NRL Radar Division. "We are looking forward to many hours of data collection and online analysis of Navy radars, as well as more detailed signal processing and analysis work back at NRL."

For more details on NRL's mission and programs, visit:

#### http://www.nrl.navy.mil

For more information on Computer I/O, visit:

http://www.computerio.com

## Signal Processing, Subsystem 3

As shown in Figure 5, Subsystem 3 is designed to retrieve data from a RAID-3 disk array and supply this data to client users over the Ethernet connection. The data may also be supplied to a DSP system for analysis. Furthermore, the system is capable of digitizing two input channels and supplying the data to the DSP processor for real-time analysis, when used in the field.

The SPARC IIi CPU running Solaris 2.7 and the Easy I/O Data Retrieval and Archiving applications is used again as a Slot 1 controller and file server for downloading data from the RAID. The interface is again supplied by a Fibre Channel PMC module. Data moves across the PMC and then across the PCI interface to local storage, or directly to the DSP system for analysis. A Pentek 4291 Quad 'C6701 floating-point processor is used for the signal analysis tasks. The data is routed through the FPDP PMC module residing on the SPARC CPU to the Pentek 6226 FPDP VIM module residing on the Pentek 4291 processor.

The Model 6211, a 2-channel 12-bit 65 MHz A/D converter VIM module also residing on the 4291, provides another

**Sussi sidT nl**

NRL Designs a COTS System ..... 1

4000 MIPS Quad 'C6203.....4

http://www.pentek.com

stəədləri datasheets

- 🔀 The latest product brochures

Model 4292 shown with Model 6210 VIM

module and Model

7110 PMC Module

- 🔀 [ στριτος] σλεγνιέψε

Designed for applications that require extremely high-speed signal processing and data transfers, Model 4292 is a Quad 'C6203 single-slot 6U VME board that delivers up to 9600 MIPS. In addition to accommodating

Pentek's broad range of VIM modules,

site which accepts industry-standard I/O

Model 4292 may be equipped with

two VIM-2 modules, either identical or

providing different functions; one VIM-4

The board is organized as four iden-

module; or one VIM-2 module in the upper position and one PMC module

tical 'C6000 processing nodes, each

in the lower position.

Model 4292 includes a PMC module

peripherals. Optionally, this site may

be occupied by a RACE++ interface.

Our Latest 'C6000 Board Features Both VIM and PMC Module Sites equipped with extensive memory

Quad 'C6203 from Pentek reaches up to 9600 MIPS

PERMIT No. 625 Newark, NJ PAID **JOATZOG .2.U 1ST CLASS MAIL** PRESORT

tables, or self-booting applications. Each processor node connects to three bidirectional FIFO memories >

The SDRAM provides a large, fast 8 MB work space operating at transfer rates up to 600 MB/sec. A 1 MB flash EEPROM provides non-volatile memory for factory boot code for self-test and initialization, and for user defined parameters,

Each 'C6203 processor node features two major memory sections: the SDRAM and the Flash memory. Both of these resources are attached to the 32-bit External Memory Interface (EMIF) bus, also known as the V-bus.

## Processor Node Resources

resources. Its architecture has been optimized for the most demanding applications in VMEbus systems.