# LVDS Digital I/O with Kintex UltraScale FPGA - XMC

#### **Features**

- Supports Xilinx Kintex Ultra-Scale FPGAs

- Supports the emerging SOSA<sup>™</sup>Technical Standard

- PCI Express (Gen. 1, 2 & 3) interface up to x8

- VITA 42.0 XMC compatible with switched fabric interfaces

- Optional front panel optical interface

- Ruggedized and conduction-cooled versions available

#### **General Information**

Model 71813 is a member of the Jade<sup>™</sup> family of high-performance XMC modules. The Jade architecture embodies a new streamlined approach to FPGA based boards, simplifying the design to reduce power and cost, while still providing some of the highest performance FPGA resources available today.

Designed to work with Pentek's new Navigator™ Design Suite of tools, the combination of Jade and Navigator offers users an efficient path to developing and deploying FPGA-based data processing IP.

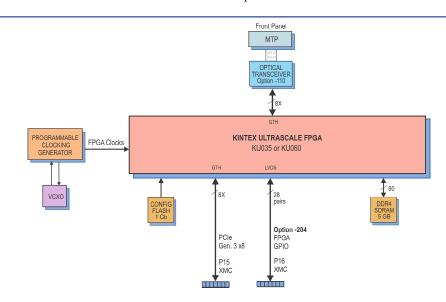

In addition to supporting PCI Express Gen. 3 as a native interface, the Model 71813 includes optional high-bandwidth optical and parallel connections to the Kintex UltraScale FPGA for custom digital I/O.

## The Jade Architecture

Evolved from the proven designs of the Pentek Cobalt and Onyx families, Jade raises the processing performance with the new flagship family of Kintex UltraScale FPGAs from Xilinx. As the central feature of the board architecture, the FPGA has access to all data and control paths. The Jade architecture organizes the FPGA as a container for data-processing applications where each function exists as an intellectual property (IP) module.

### **Extendable IP Design**

For applications that require specialized functions, users can install their own custom IP for data processing. The Pentek Navigator FPGA Design Kits include the board's entire FPGA design as a block diagram that can be edited in Xilinx's Vivado tool suite.

In addition to the block diagrams, all source code and complete IP core documentation is included. Developers can integrate their own IP along with the wide range of IP functions contained in the Navigator IP library, or use the Navigator kit to completely replace the Pentek IP with their own.

## Xilinx Kintex UltraScale FPGA

The Kintex UltraScale FPGA site can be populated with a range of FPGAs to match the specific requirements of the processing task, spanning the KU035 through KU060.

The KU060features 2760 DSP48E2 slices and is ideal for modulation/demodulation, encoding/decoding, encryption/decryption, and channelization of the signals between transmission and reception. For applications not requiring large DSP resources or logic, a lower-cost FPGA can be installed.

# Support for the SOSA Technical Specification

Option -204 installs the P16 XMC connector with 28 pairs of LVDS connections to the FPGA for custom I/O. When mounted on a compatible single board computer, the 71813 provides a customizable I/O signal status and control interface to support the emerging Sensor Open Systems Architecture (SOSA $^{TM}$ )Technical Standard.

# **Front Panel Optical Interface**

The 71813 can be optionally configured with a front panel MPO optical connector for supporting four 12Gbps lanes to the FPGA. With user installed FPGA IP, the 71813 can be used as an optical interface for 10GigE, 40GigE, Aurora, as well as custom protocols

# LVDS Digital I/O with Kintex UltraScale FPGA - XMC

#### **Memory Resources**

The 71813 architecture supports a 5 GB bank of DDR4 SDRAM memory. User-installed IP along with the Pentek-supplied DDR4 controller core within the FPGA can take advantage of the memory for custom applications.

## **SPARK Development Systems**

The SPARK Development Systems are fully-integrated platforms for Pentek Cobalt, Onyx, Jade and Flexor boards. Available in a PCIe rackmount (Model 8266), a 3U VPX chassis (Model 8267), or a 6U VPX chassis (Model 8264), they were created to save engineers and system integrators the time and expense associated with building and testing a development system. Each SPARK system is delivered with the Pentek board(s) and required software installed and equipped with sufficient cooling and power to ensure optimum performance.

#### ➤ PCI Express Interface

The Model 71813 includes an industrystandard interface fully compliant with PCI Express Gen. 1, 2 and 3 bus specifications. Supporting PCIe links up to x8, the interface includes multiple DMA controllers for efficient transfers to and from the board.

# **Specifications**

Field Programmable Gate Array

**Standard:** Xilinx Kintex UltraScale XCKU035-2

**Option -084:** Xilinx Kintex UltraScale XCKU060-2

#### Custom I/O

**Option -204:** Installs the XMC P16 connector with 28 LVDS pairs to the FPGA **Option -110:** Installs a front panel optical MPO connector with an 4X gigabit serial link to the FPGA

#### Memory

Type: DDR4 SDRAM

Size:5GB

**Speed:** 1200 MHz (2400 MHz DDR)

**PCI-Express Interface**

PCI Express Bus: Gen. 1, 2 or 3: x4 or x8

**Environmental**

Standard: L0 (air cooled)

Operating Temp: 0° to 50° C Storage Temp: -20° to 90° C **Relative Humidity:** 0 to 95%, non-condensing

Option -702: L2 (air cooled)

Operating Temp: -20° to 65° C Storage Temp: -40° to 100° C Relative Humidity: 0 to 95%, non-

condensing

Option -713: L3 (conduction cooled) Operating Temp: -40° to 70° C Storage Temp: -50° to 100° C Relative Humidity: 0 to 95%, noncondensing

**Size:** XMC module 2.910 in x 5.870 in (74.00 mmx 149.00 mm)

# **Ordering Information**

Model Description

71813 LVDS Digital I/O with

Kintex UltraScale FPGA

- XMC

#### Options:

- 084 XCKU060-2 FPGA

- 204 LVDS FPGA I/O through

P16 connector

- 702 Air cooled, Level L2

- 713 Conduction cooled,

Level L3

Contact Pentek for complete specifications of rugged and conduction-cooled versions